Scientists at Tokyo Tech have developed an advanced phase-locked loop (PLL)1 frequency synthesizer that can drastically cut power consumption. This digital PLL could be an attractive building block for Bluetooth Low Energy (BLE) and other wireless technologies to support a wide range of Internet of Things (IoT) applications.

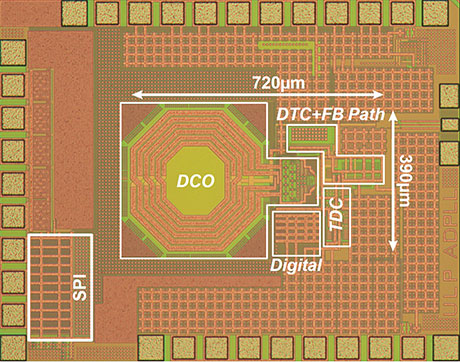

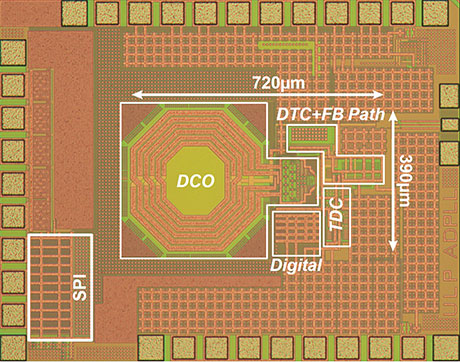

Figure 1. An image of the new digital PLL

The proposed fractional-N DPLL occupies an area of 0.25 mm2 in 65-nanometer CMOS.

As a key building block of wireless communication systems, frequency synthesizers need to satisfy demanding requirements. Although analog PLL frequency synthesizers have been the standard for many years, engineers in the IoT industry are increasingly turning their attention to so-called digital PLLs (DPLLs) to achieve ultra-low power operation.

Kenichi Okada, associate professor at Tokyo Tech's Department of Electrical and Electronic Engineering and his group now report a fractional-N DPLL2 that achieves a power consumption of only 265 microwatts(μW), a figure that is less than half the lowest power consumption achieved to date (980 μW). (Table 1)

Table 1. Comparison table with state-of-the-art fractional-N DPLLs.

The researchers found that overall power consumption could be greatly reduced by using an automatic feedback control system. "This automatic-switching feedback path consumes a power of 68 μW, which leads to a power consumption of 265 μW for the whole DPLL," Okada says.

The promising DPLL could go on to be used as a component for processors, memories and a vast new range of IoT devices that will be expected to be both cost-effective and eco-friendly by running on ultra-low power. Okada notes that early experiments show the DPLL could extend battery life by four times.

This paper is partially based on results obtained from a project commissioned by the New Energy and Industrial Technology Development Organization (NEDO).

This work is being presented in the Frequency Synthesizers session at the 2019 International Solid-State Circuits Conference (ISSCC), the world's leading annual forum on solid-state circuits and systems-on-a-chip.

(ISSCC), the world's leading annual forum on solid-state circuits and systems-on-a-chip.

1 Phase-locked loop (PLL)

A control system used as a basic component of many radio, wireless and telecommunication technologies. The present study draws on the ability of PLLs to generate a stable frequency at multiples of an input frequency.

2 Fractional-N DPLL:

An emerging class of digital PLLs that are of much interest as they can help improve phase noise.

Reference

Authors : |

Liu, H. et al.

Tokyo Institute of Technology, Japan |

Session : |

Session 16: Frequency Synthesizers |

Session title : |

A 265μW Fractional-N Digital PLL with Seamless Automatic Switching Subsampling/Sampling Feedback Path and Duty-Cycled Frequency-Locked Loop in 65nm CMOS |

Conference : |

|

DOI : |

|

- *

- This article has been updated to add DOI on March 26.

. Any information published on this site will be valid in relation to Science Tokyo.