東工大ニュース

東工大ニュース

公開日:2015.03.20

不揮発性パワーゲーティングがCMOSロジックシステムの待機時電力削減に威力

―不揮発性SRAMを用いた記憶回路で実証―

東京工業大学像情報工学研究所の菅原聡准教授、周藤悠介特任助教、山本修一郎特任助教らの研究グループは、公益財団法人神奈川科学技術アカデミー(KAST;カスト)と共同で、不揮発記憶を用いたCMOSロジックの待機時電力削減アーキテクチャとして期待されている不揮発性パワーゲーティング(NVPG[用語1])とノーマリオフ(NOF[用語2])について、そのエネルギー性能の解析を行い、NVPGの有効性を明らかにした。マイクロプロセッサやシステム・オン・チップ(SoC)に搭載される上位階層の記憶回路を想定し、不揮発性メモリ素子である強磁性トンネル接合(MTJ[用語3])とCMOSとの融合回路から構成される不揮発性SRAMについて高精度シミュレーションによるベンチマークを行った。その結果、待機時電力の削減効率は、不揮発記憶に要する過剰なエネルギーと動作上待機状態にならざるを得ないセル部分における待機時エネルギーとの拮抗によって決まるが、記憶回路へのアクセス回数が多いマイクロプロセッサやSoCへの応用の場合ではNVPGの方が圧倒的に有利になることを明らかにした。

研究成果は3月10日からフランス・グルノーブルで開催されたヨーロッパで最大級の集積回路に関する国際会議DATEで3月11日に発表された。

パーソナルコンピュータやサーバに搭載されているマイクロプロセッサや、スマートフォンなどの携帯機器に搭載されているシステム・オン・チップ(SoC)などのCMOSロジックシステムでは、トランジスタの微細化と高密度集積化によって高性能化を実現してきた。この一方で、トランジスタのリーク(漏れ)電流によってシステムの待機(スタンバイ)時に消費するスタンバイ電力が著しく増大し、重大な問題となっている。

このような待機時電力はロジックシステムにおける待機状態の回路ブロックへの電源供給を遮断することで削減できる(これがパワーゲーティングと呼ばれる技術である)。しかし、従来のCMOSロジックシステムでは電源遮断によってシステム内に存在する重要なデータ(情報)が失われるといった問題があるために、この方法を用いる場合には制約が大きく、効果はあるもののその本来の能力を十分に発揮できていない状況にあった。近年、不揮発記憶を利用して、ロジックシステムの電源遮断を効果的に行い高効率に待機時電力を削減する方法がいくつか提案されている。

その一つが菅原聡准教授らの研究グループが提案した不揮発性パワーゲーティング(NVPG)である。通常、CMOSロジック内で用いられる高速動作可能な記憶回路(SRAMやフリップフロップなどと呼ばれる双安定記憶回路)は電源遮断によって記憶内容を失ってしまうが、このような双安定記憶回路に不揮発性メモリ素子を付加することで、電源遮断を行ってもデータを保持できるようにできる。同研究グループの提案した不揮発性双安定回路[用語4]では、CMOSロジックが通常の動作を行っているときには、不揮発記憶は用いずに通常の双安定記憶回路として動作し、電源遮断を行うときにだけ不揮発記憶を行うところに特徴がある。これによって、通常動作には影響を与えず、高効率にエネルギーを削減できるNVPGが実行できる。

これとは別の待機時電力削減アーキテクチャとしてノーマリオフ(NOF)がある。これはデータの記憶に常に不揮発記憶を用いる。このため、通常は電源遮断しておき、必要なときにのみ記憶回路に通電して、可能な限り待機時電力を削減する。しかし、通常、不揮発記憶には従来のCMOS構成の記憶回路に比べて大きなエネルギーを要し、また、動作速度も遅いといった問題がある。したがって、情報処理量が小さく、待機時間が非常に長いマイクロコントローラなどに用いる場合にはメリットがあるが、マイクロプロセッサやSoCのように情報処理量が多く演算時間の長い応用には適していないと考えられる。しかし、現状では、これらのアーキテクチャの理解不足による誤った見解も多い。

この原因の一つは、それぞれのアーキテクチャがそれぞれ異なった不揮発性記憶回路を用いて提案されており、システマティックな比較・検討が行われていなかったことが大きい。また、不揮発性記憶回路の導入による効果を従来の揮発性の記憶回路の場合と比較してそのメリットを判断することも重要になるが、このような検証もほとんど行われていない(これには後に述べるBreak-even timeと呼ばれる指標を用いることが重要となる)。

同研究グループの提案している不揮発性双安定記憶回路は、どちらのアーキテクチャにも用いることが可能なことから、これを用いて高精度シミュレーションから二つのアーキテクチャに関する性能を従来の双安定記憶回路と比較し、定量的評価を行った。

本研究グループが提案している不揮発性SRAM(NV-SRAM)を用いてNVPGおよびNOFのアーキテクチャを検討した。マイクロプロセッサやSoCにおける上位階層のキャッシュメモリを想定して、それぞれのアーキテクチャの特性を解析した。

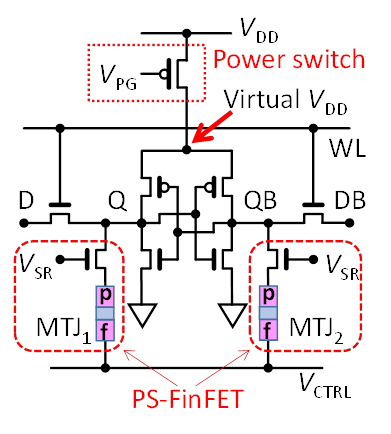

図1に解析に用いたNV-SRAMセルの構造を示す。通常のSRAMセルにトランジスタを介して、不揮発性メモリ素子である強磁性トンネル接合(MTJ)を接続しているところに特徴がある。このトランジスタによって、通常動作時(不揮発記憶を用いない双安定回路のみの読み出し/書き込み動作時)にはMTJをSRAMから電気的に切り離すことが可能となる。また、NV-SRAMに接続されたパワースイッチでセルへの電源遮断を行う。このNV-SRAMセルを用いて、メモリアレイ(Mビット×Nライン)および周辺回路を構成してシミュレーションを行った。

図1. NV-SRAMセルの回路構成

トランジスタを介してMTJを通常のSRAMセルの記憶ノードに接続してある。パワースイッチによってセルへの電源遮断ができる。

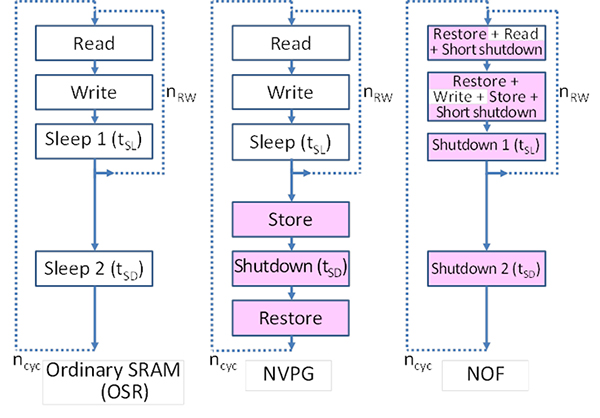

図2に評価に用いたNVPGおよびNOFのベンチマークのシーケンスを示す。NVPGでは電源遮断を行うときにだけ、MTJへの書き込みを行い、短い時間の待機時はスリープモードとした(双安定回路のデータが消えない程度に供給電圧を絞る動作。パワーゲーティングほどではないが待機時電力の削減に効果がある)。NOFでは、データの書き込みには常にMTJへの書き込みを行い、待機時および毎回の読み出し後と書き込み後電源遮断を行っている、比較のための通常のSRAMでは、待機時はすべてスリープモードを用いた(現在、SRAMにスリープモードを導入することは常套手段となっている。SRAMとの性能比較を行う場合、SRAMにはスリープモードによる待機時電力の削減の効果を含めておくことが重要である。スリープモードのないSRAMとの比較は実用上の意味を持たない)。

図2. ベンチマークシーケンス

NVPGではセルアレイの全ビットを読み出し/書き込み後、時間tSLのスリープモードを実行する。これをnRW回繰り返し、MTJに書き込み(ストア)してから時間tSDシャットダウンし、復帰(リストア)する。通常のSRAM(OSR)では、待機時はすべてスリープモード、NOFでは待機時および読み/書き後はすべでシャットダウンしている。

以上の回路構成とアーキテクチャを用いて、高精度の回路シミュレーションを行った。CMOSデバイスについては最先端のCMOSデバイスであるFinFET(立体的なチャネルを持つ高性能の電界効果型トランジスタ)のPredictive Technology Modelを、MTJについては同研究グループの開発した高精度マクロモデルを用いた。

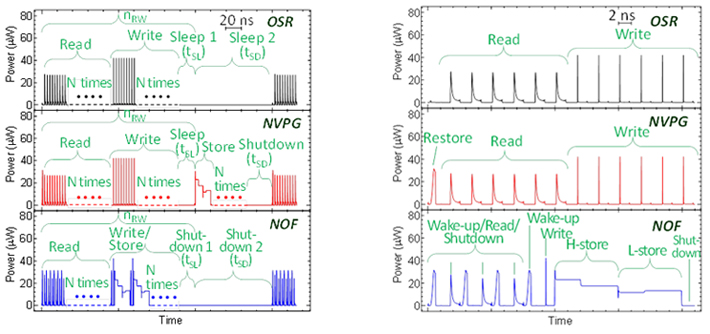

図3に動作波形を示す。NVPGでは、通常の(双安定回路部のみの)SRAM動作と、MTJへ書き込みを行う不揮発記憶の動作を分離できる。したがって、NVPGにおける通常の読み出しと書き込みはSRAMと同じ速度で実行できる。一方、NOFでは、通常動作と不揮発記憶動作を分離せず常に不揮発記憶を用いる。このため、不揮発記憶の必要のない通常の書き込みにも不揮発記憶を実行しなければならず、動作速度が大きく劣化する。さらに、毎回の読み出し時にも復帰動作と電源遮断を行うため、動作速度が低下する。また、この余計な動作に要する電力も余分に消費している。NOFではこのような動作速度の劣化があっても頻繁に電源遮断を行うことによって、エネルギー的にメリットが生じると考えられているが、以下に示すようにこれは正しくない。

図3. 各アーキテクチャによるNV-SRAMとSRAMの動作波形

左図は図2のシーケンスにしたがって動作させた場合の波形。右図はその拡大図である。NVPGでは通常のSRAMと同じ速度で読み出しと書き込みが実現できる。NOFでは読み出しや書き込みの度に復帰およびシャットダウン動作するため、動作速度が劣化するだけでなく、リストアやストアに伴う余計なエネルギー消費を生じる。

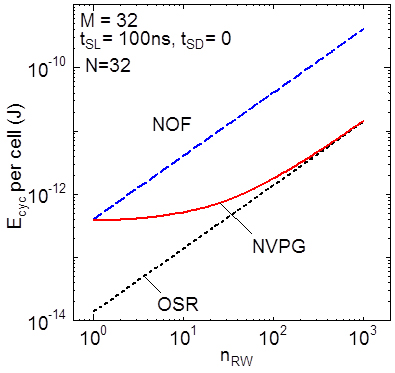

図4にnCYC=1における消費エネルギーEcycの読み出し/書き込み動作サイクル数nRW依存性を示す(nCYC、nRWは図2参照)。ここでは、セルのシャットダウン時間tSD(図2参照)を零としている。この条件は、不揮発記憶動作(ストア動作)と電源遮断からの復帰動作(リストア動作)の影響を評価するのに効果的である。NVPGではEcycはnRWの増加とともに通常のSRAMのエネルギーに漸近することがわかる。すなわち、ストア、リストアの影響はnRWの増加とともに消失する。これは同研究グループの提案しているNVPGの特徴の一つである。

図4. 消費エネルギーEcycのnRW依存性

ここではストアとリストアの効果を明らかにするためにtSD=0とした。NVPGのEcycはnRWの増加とともに通常のSRAMの場合に漸近するが(ストアとリストアによる過剰なエネルギーの効果はnRWの増加とともに薄れる)、NOFではこのような効果はない。

一方、NOFセルでは、このような依存性は見られず、しかも、消費エネルギー自体が通常のSRAMに比べて大きい。この特徴はシステムが電源遮断時に不揮発記憶を必要とする容量(プロセッサコアでは数K~10Kバイト程度)を変化させても変わらない。情報処理量が多く、メモリアクセスも極めて多い上位階層のキャッシュでは、NVPGのこの特徴は特に重要になる。まとまった演算処理の終了後に電源遮断を行うNVPGはマイクロプロセッサのコアやSoCのパワーゲーティングに有効であることがわかる。

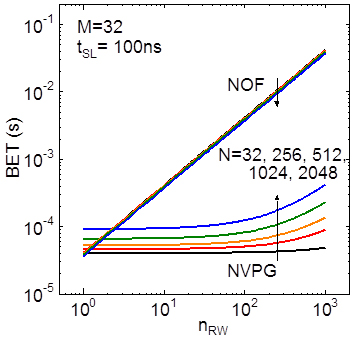

図5に、Break-even time (BET[用語5])のnRW依存性を示す。BETは電源遮断によってエネルギーを削減できる最低の電源遮断時間である。NOFでは、nRWの増加にともない、BETが大きく増大している。これは、不揮発記憶と電源遮断を繰り返すことで、エネルギー削減の効果が小さくなることを示している(nRWの増加にともない、エネルギー削減のために、より多くの電源遮断時間が必要になる)。一方、NVPGでもBETはnRWに依存するが、その依存性は小さく、特にnRWの増加に伴うBETの増大は、NOFに比べてはるかに小さい。したがって、NVPGでは電源遮断によってより効果的にエネルギーを削減できる。さらに、NVPGでは我々の提案しているストアフリーシャットダウン(既書き込みのデータと同じデータは書き込まない不揮発記憶のアーキテクチャ)の導入によってBETはさらに大きく削減できる。したがって、細粒度のNVPGが可能となる。

図5. Break-even time(BET)のnRW依存性

NOFではnRWの増加とともにBETは大きく増加する(最低限必要なシャットダウンの時間が延びる)。一方、NVPGでは、nRWの増加にとともなうBETの増大は緩やかである。NVPGは情報処理量の多いマイクロプロセッサのコアやSoCのスタンバイ電力の削減に有効である。

NOFにおいて、十分なエネルギーの削減効果を実現するためには、不揮発記憶に必要となる書き込みのエネルギーをSRAMより小さくすることが重要となる。今回の解析では不揮発性メモリ素子として用いたMTJは他の不揮発性メモリ素子に比べて、比較的に低エネルギーで書き込みが可能な素子であるが、SRAM以下に低減するのは容易ではない。MTJでは書き込み電流を小さくすると、スイッチングのエラーレートは増大する。また、マイクロプロセッサやSoCでは動作時のチップ温度はかなり高くなるが、エラーレートはチップ温度の上昇によっても増大する。さらに、トランジスタのバラツキ程度(小さくない)またはそれ以上にMTJの特性バラツキもあることを考えるとMTJの書き込みエネルギーをこのように小さく下げることは相当に困難であると考えられる。このことと、図4と図5に述べた特性を考慮すれば、マイクロプロセッサやSoCへの応用ではNVPGの方が圧倒的に有利であることがわかる。

現在のマイクロプロセッサやSoCの高性能化ではマルチコア化が必須の技術になっているが、今後はさらに大規模なマルチコア化(メニーコア化)が重要になってくる。この一方でダークシリコンと呼ばれる各コアの消費エネルギーのため同時に動作できるコアの数に制限が加わるという問題も発生する。このような問題では各コアの低消費電力化がより重要となるが、NVPGはこのようなメニーコアのプロセッサやSoCに極めて有効な待機時電力削減アーキテクチャとなる。一部に、コアでは従来のCMOS技術のみによるパワーゲーティングのみで十分であるという意見があるがこれは正しくない。従来技術のみではダークシリコンの問題は解決できない。従来のCMOS技術以上に細粒度で電源遮断することが可能となるNVPGが重要となる。

用語説明

[用語1] 不揮発性パワーゲーティング(NVPG) : マイクロプロセッサやSoCにおけるメモリシステムに不揮発の機能を付加し、高効率の待機時電力の削減が可能なパワーゲーティングを実現するアーキテクチャで、菅原准教授らの研究グループによって提案された。通常動作と不揮発記憶の動作を分離することで、コア内部まで不揮発化をすることが可能となり(コア内のすべての記憶回路を不揮発化する必要はない)、現状のパワーゲーティングでは実現できない最適な空間的・時間的粒度のパワーゲーティングを実行できる。このため、待機時電力の削減効率を極限まで高くできる。通常動作/不揮発記憶の機能分離によって、マイクロプロセッサやSoCの既存アーキテクチャとの整合性も高い。NVPGを実現するためには不揮発性SRAM(NV-SRAM)や不揮発性フリップフロップ(NV-FF)などの不揮発性双安定回路が必要であるが、通常動作と不揮発記憶の動作を完全に分離できる回路構成であることが必要となる。ロジックシステムに不揮発の機能を取り入れる発想は古くからあるが、パワーゲーティングに不揮発記憶を導入してパワーゲーティングの能力を極限まで引き出そうという試み(NVPG)は同研究グループによって初めて提案された。

[用語2] ノーマリオフ(NOF) : NVPGはノーマリオフ(NOF)としばしば混同されることがあるが、NVPGはこれとは以下に示すように全く異なる。NOFは不揮発性メモリを用いて、システムの電源遮断を頻繁に行い、またできるだけ高速に電源遮断状態からリブート(再起動)するアーキテクチャである(高性能化したインスタントオンともいえる)。オリジナルのアイデアではメモリシステムのすべてを不揮発化して頻繁にシステムのオン/オフ繰り返すアーキテクチャであった。したがって、システムのランタイムに待機時電力の削減の効果がなく、この削減のためにはパワーゲーティングを併用する必要があった。最近の構成では、メモリシステムの上位階層は不揮発化を行わないで、通常のパワーゲーティングを行うものに変更している。このシステムでは従来のパワーゲーティングの問題はそのまま残る。

[用語3] 強磁性トンネル接合(MTJ) : 薄い絶縁性薄膜(トンネル障壁)を2つの強磁性電極で挟んだトンネル接合構造の2端子素子で、不揮発性メモリMRAMの記憶素子に用いられる。強磁性電極の相対的な磁化状態が平行な場合と、反平行の場合で素子の電気抵抗が異なる。また、100nm程度以下に微細化されたMTJではスピン注入磁化反転と呼ばれる現象によって、磁場を用いることなく、MTJを流れる電流によって電気的に磁化状態を変化させることができる。

[用語4] 不揮発性双安定記憶回路(不揮発性SRAM(NV-SRAM)、不揮発性フリップフロップ(NV-FF)) : NV-SRAMやNV-FFなどの不揮発性双安定回路はこれまでにもインバータループに不揮発性メモリ素子を直接接続する方法がいくつか提案されてきたが、このような従来の方式ではインバータループに接続された不揮発性メモリ素子が、通常の双安定回路の動作に悪影響を与え、動作速度の劣化や消費電力の増大、さらにはバラツキ耐性やノイズマージンの減少など回路性能の劣化を生じる。このため、同研究グループが提案しているように通常動作と不揮発記憶の動作を完全に分離できる回路構成が必要になる。同研究グループの提案した不揮発性双安定回路は、インバータループ外にトランジスタを介して不揮発性メモリ素子を接続するため、インバータループと不揮発性メモリ素子を電気的に分離できる。したがって、通常のSRAM動作やフリップフロップ動作に影響を与えることなく、不揮発記憶/NVPG動作を実行できる。

[用語5] Break-even time(BET、損益分岐時間) : NVPGやNOFでは不揮発記憶を行うが、このとき大きなエネルギー消費を伴う。また、セルの構成によってはリーク電流なども従来の記憶回路に比べて増加していることがある。このような不揮発性記憶回路の導入に伴う余計なエネルギー消費があるため、闇雲に不揮発性記憶回路を用いると、むしろエネルギー消費を増大させてしまうことがある。“不揮発”=“低消費電力”といわれることがあるが、これは大きな間違いである。一般に“不揮発”≠“省エネ”であることに注意する必要がある。不揮発性記憶回路の導入に伴う余計なエネルギー消費をシャットダウンによって埋め合わすことができる最低限必要なシャットダウン時間がBreak-even time (BET)である。このBETは損益分岐時間と呼ばれることもある。BETを短くすることで時間的・空間的細粒度のNVPGやNOFが実現可能となる。BETの算出にはいくつか方法があるが、最も重要なものは既存の記憶システムと新しく導入した記憶システムとの比較から求めるBETである。新たに導入する記憶回路にどのような回路構成や駆動方式を用いていても、記憶回路であれば必ずBETを算出できる。例えばSRAMを不揮発性メモリMRAMで置き換えてもBETは算出できる。従来のCMOSロジックシステムにおいてはBETの概念はすでに用いられていたが、不揮発記憶を使ったパワーゲーティングにこの概念を導入したのは同研究グループが初めてである。

論文情報

掲載誌 : |

18th Design, Automation and Test in Europe (DATE15), Grenoble, France, March 9-13, 2015, paper 7.7.3. |

論文タイトル : |

Comparative study of power-gating architectures for nonvolatile FinFET-SRAM using spintronics-based retention technology |

著者 : |

Y. Shuto, S. Yamamoto, S. Sugahara

|

問い合わせ先

東京工業大学 像情報工学研究所

准教授 菅原聡

Email : sugahara@isl.titech.ac.jp

東京工業大学 像情報工学研究所

特任助教 周藤悠介

Email : shuto@isl.titech.ac.jp

Tel : 045-924-5456

Fax : 045-924-5456

KASTの事業に関して

公益財団法人神奈川科学技術アカデミー

イノベーションセンター・研究支援グループ

後藤・前川

Email : res@newkast.or.jp

Tel : 044-819-2034

取材申し込み先

東京工業大学広報センター

Email : media@jim.titech.ac.jp

Tel : 03-5734-2975

Fax : 03-5734-3661