Realizing Compact, Low-Cost, High-Speed Radio Communication Systems for the IoT Age

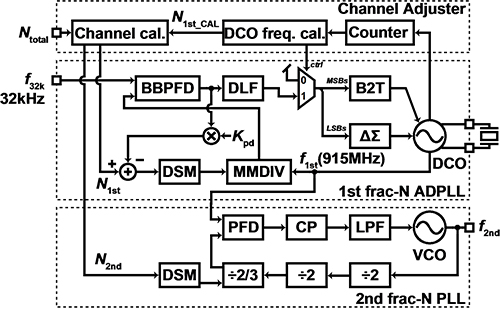

In collaboration with the National Institute of Information and Communications Technology (NICT), Associate Professor Hiroyuki Ito and Professor Kazuya Masu, et.al., of the Tokyo Institute of Technology, developed a new algorithm and circuit technology allowing high-frequency piezoelectric resonators[1] to be used for phase locked loops (PLL)[2]. It was confirmed that these operate with low noise and have an excellent Figure of Merit (FoM)[3] compared to conventional PLLs.

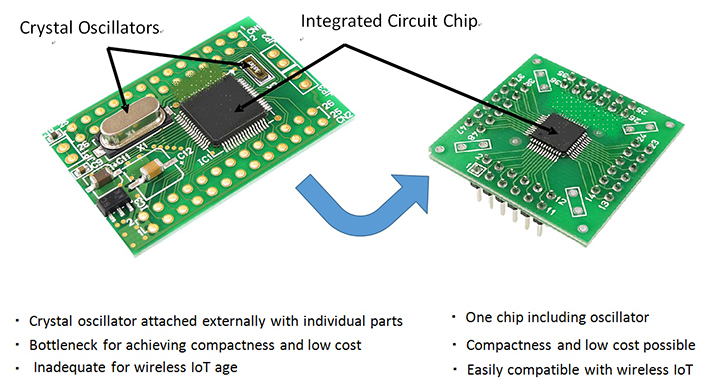

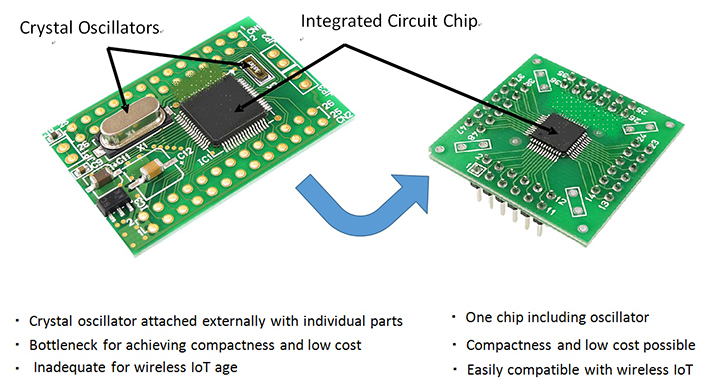

This technology allows high-frequency piezoelectric resonators to be used in place of crystal oscillators[4] which was a problem for realizing compact and low-cost radio modules. This greatly contributes to the creation of compact, low-cost, high-speed radio communication systems for the IoT age. High-frequency piezoelectric resonators are compact, can be integrated, have an excellent Q value[5], and oscillators that use these have excellent jitter performance[6]. High-frequency piezoelectric resonators had greater issues with resonance frequency variance and temperature dependability compared to crystal resonators. However, these issues were resolved by the development of a PLL that uses a channel adjustment technique, which is a new algorithm.

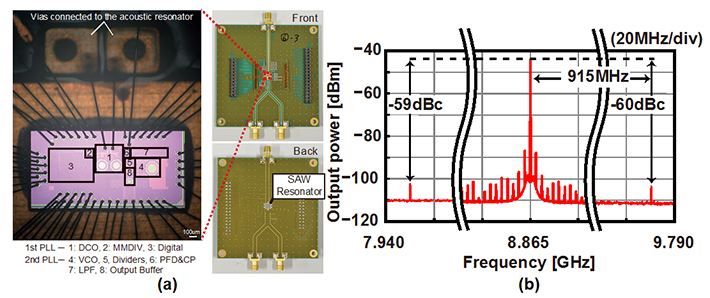

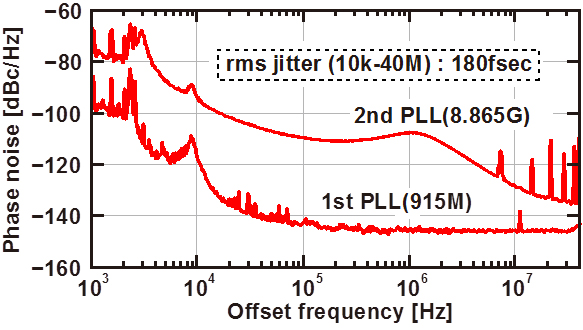

A prototype was fabricated by a silicon CMOS process with a minimum line width of 65 nm, and a maximum frequency output of approximately 9 GHz was achieved with a phase fluctuation of only 180 femtoseconds[7]. Power consumption was 12.7 mW. This performance is equivalent to a PLL Figure of Merit (FoM) of -244 dB[8], and it has the world's top-class performance as a fractional-N PLL[9]. This can contribute to the realization of compact, low-cost, high-speed radio communication systems.

The study results will be announced in local time June 17 in the "2016 Symposium on VLSI Circuits," to be held in Hawaii from June 14 .

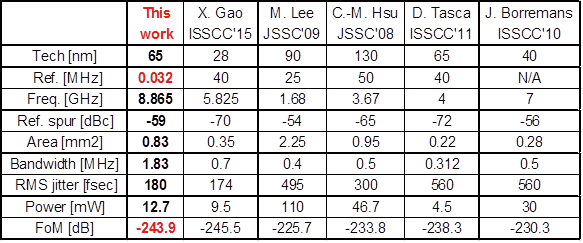

Figure 1. Conceptual Schematic Diagram of the Application Effect of this Achievement

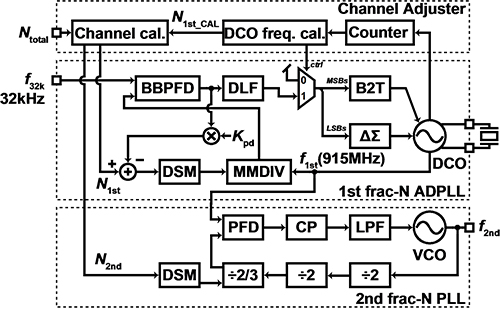

Figure 2. Block Diagram of the Proposed PLL

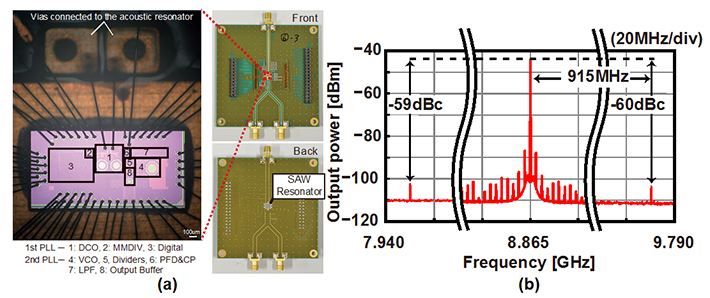

Figure 3. Photo of the Chip and Output Signal Spectrum

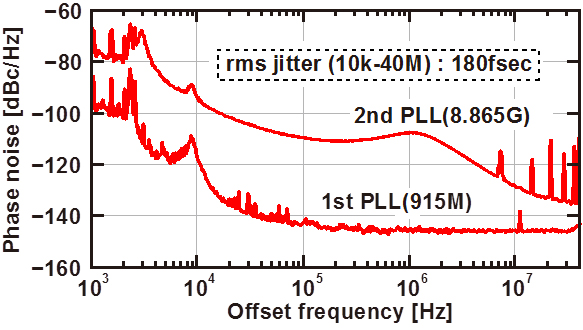

Figure 4. Phase Noise Measurement Results

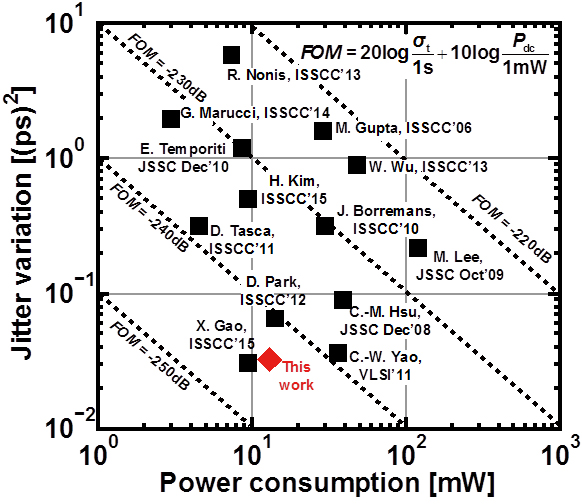

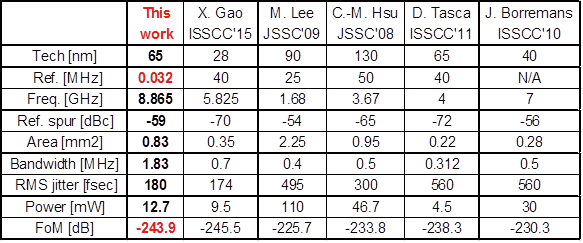

Figure 5. Performance Comparison with Conventional Fractional-N PLLs

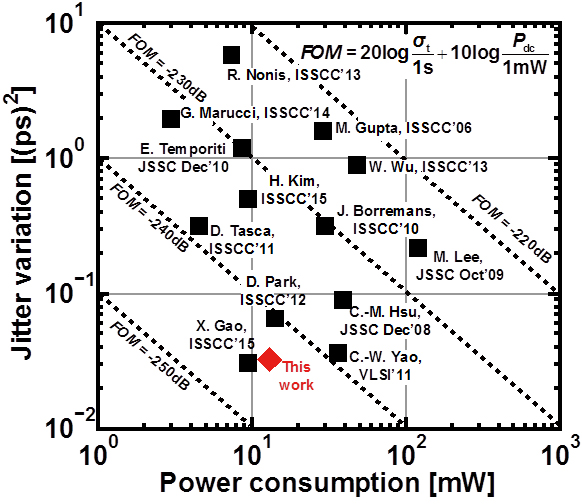

Figure 6. FoM Comparison with Conventional Fractional-N PLLs

Explanations of Technical Terms

- [1]

- Piezoelectric Resonator

Resonator that uses a piezoelectric film and includes FBAR (Film Bulk Acoustic Resonators) and SAW (Surface Acoustic Wave) resonators. These have a high Q value in the GHz range, so these are considered being used for low noise oscillators.

- [2]

- Phase Locked Loop (PLL)

Electric circuit that generates a signal at an arbitrary frequency where the phase is synchronized with an external input signal (reference signal) due to feedback control.

- [3]

- Figure of Merit (FoM)

Index for comparing the performance of oscillation circuits. The lower this numerical value, the better the performance.

FoM = Phase Noise - 20 log10 (Oscillating frequency / Offset frequency) + 10 log10 (Power consumption [mW])

- [4]

- Crystal Oscillator

Oscillator that uses a crystal as the piezoelectric material for the resonator, and is widely used as a reference signal source in radio communication systems. These have much higher frequency precision and stability than high-frequency piezoelectric resonators.

- [5]

- Q Value

Value that expresses the sharpness of the resonance peak for resonance circuits. The higher this value, the sharper the peak. The Q value of crystal resonators is several 10,000, the Q value of piezoelectric resonators is several thousand, and the Q value of general LC resonators is in the tens.

- [6]

- Jitter

Fluctuation component generated in the time-base direction of the signal. Noise.

- [7]

- Femto- (f)

Prefix in the International System of Units that indicates 10-15.

- [8]

- dB (Decibel)

Unit used when a physical quantity is described as a level indication in the electrical engineering field, etc.

- [9]

- Fractional-N PLL

PLL that can change the output signal by fraction multiplication of the reference signal for an integer dividing PLL, which can only output an integral multiplication frequency of the reference signal input to the PLL. The merit is that an arbitrary frequency can be generated in the frequency band.

Reference

Authors: |

Sho Ikeda1, Hiroyuki Ito1, Akifumi Kasamatsu2, Yosuke Ishikawa1, Takayoshi Obara1, Naoki Noguchi1, Koji Kamisuki1, Yao Jiyang1, Shinsuke Hara2, Dong Ruibing2, Shiro Dosho1, Noboru Ishihara1, Kazuya Masu1 |

Title: |

An 8.865-GHz -244dB-FOM High-Frequency Piezoelectric Resonator-Based Cascaded Fractional-N PLL with Sub-ppb-Order Channel Adjusting Technique |

Conference: |

Session 22 — Clock and Frequency Synthesis, The 2016 Symposium on VLSI Circuits |

Affiliations: |

1Institute of Innovative Research, Tokyo Institute of Technology

2Natinal Institute of Information and Communications Technology |

. Any information published on this site will be valid in relation to Science Tokyo.