東工大ニュース

東工大ニュース

公開日:2021.02.19

東京工業大学 工学院 情報通信系の原祐子准教授らは、IoTの高度化において必要不可欠になる小型・省電力性を兼ね備えた新たなプロセッサ[用語1]を設計し、そのプロセッサの大規模集積回路(LSI)の開発に成功した。ヘルスケアデバイスを想定した異常検出においては、商用の最小プロセッサであるARM Cortex-M0の1.4倍高速でありながら電力効率は2.7倍、エネルギー効率は3.8倍を達成した。

既存のプロセッサは多様化するアプリケーションのニーズに合わせ、大規模化と消費電力の増加が進んでいるが故に、小型デバイスのIoT化に対してはオーバースペックである。本研究では小型エッジ端末[用語2]で必要な計算を実用的な時間で処理するための機能に限定することで、従来プロセッサに比べて回路面積を大幅に削減し、小型化と省電力化を両立するアーキテクチャ「SubRISC+」を開発した。65 nm CMOSプロセス[用語3]を用いたプロセッサLSIは、1 mm×1 mmと小型、かつ、わずか77.0 µWの消費電力で、異常検出やデータ探索などの実用的なアプリケーションをリアルタイムに処理することができる。

開発したプロセッサは、原准教授らが2020年7月3日付で米国の科学誌「IEEE Access」に発表した研究成果を基に実機を試作し評価したところ、良好な結果が得られたものである。プロトタイプのサンプル配布も検討しており、今後はさらに用途の拡張と実用化を目指してチップの試作と開発を進めていく。

モノのインターネット(Internet of Things; IoT)の発展に伴い、多種多様なデバイスがデータをセンシングし、ネットワークに接続されるようになっている。現在のIoTで多く用いられる形式はクラウドコンピューティング[用語4]だが、センシングデータに対してリアルタイムに計算しデバイスを制御するために、今後はエッジコンピューティング[用語5]の普及が必要不可欠である。しかし、既存の組み込みシステム[用語6]向けのプロセッサは消費電力の点から、エッジコンピューティングへの展開は難しいということが課題となっている。

本研究では、次世代IoTで重要となるエッジコンピューティングの普及を加速させるために必要な小型・省電力な組み込みプロセッサを新たに構築し、そのLSIの開発に成功した。近年の組み込みシステム向けプロセッサはアプリケーションの多様化にともない、機能(命令数)が増え、回路面積や消費電力が増大する傾向にあった。

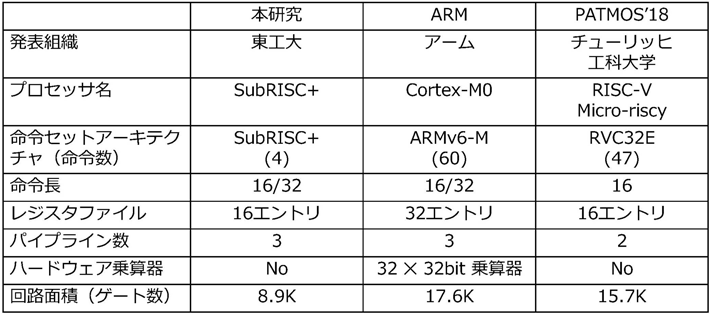

既存の32ビット組み込みプロセッサでは極めて小規模なものでさえ、約50種の命令を扱う。しかし、IoTの小型エッジ端末では、異常検出などの比較的単純な処理で十分な場合もあり、既存プロセッサではオーバースペックであるという問題があった(表1)。これに対し、本研究は小型エッジ端末で必要な計算を実用的な時間で処理するための機能に限定することで、回路面積を大幅に削減し、小型化と省電力化を両立するプロセッサLSIを開発した。

表1. 小型マイクロプロセッサの比較

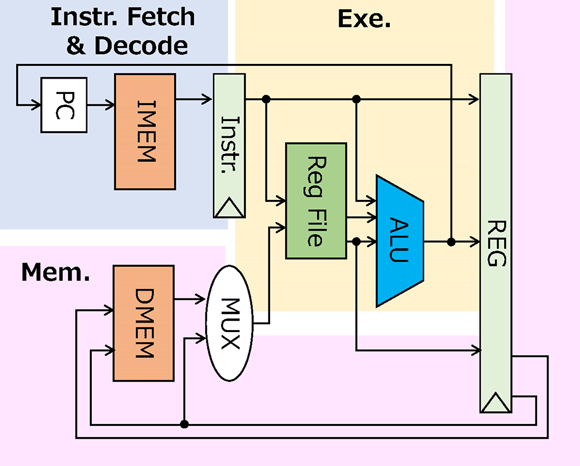

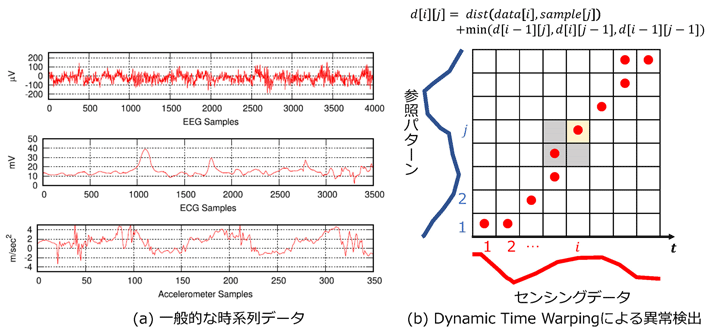

本研究で開発した組み込みプロセッサは、減算・シフト・論理演算・メモリアクセスの4種類の命令のみから成るRISCプロセッサ[用語7]であり、減算結果に応じて条件分岐するという特徴を持つことから、このアーキテクチャ(図1)を「SubRISC+」と名付けた。近年は心電図・加速度などのデータ(図2a)のセンシング機能が、ウェアラブルデバイスや携帯端末に搭載されることが増えている。SubRISC+は、それらのデータから異常検出やデータ探索する軽量アルゴリズム[用語8]をリアルタイムに処理し、警告などの限られたデータのみを送信する用途を想定している。なお、SubRISC+はチューリング完全[用語9]であるため、これらの用途以外のあらゆるプログラムを処理することができる。

図1. SubRISC+アーキテクチャ

図2. SubRISC+に実装できる軽量アルゴリズムの一例

(a)ウェアラブルデバイスなどから取得されるデータの例。上から脳波、心電図、加速度を示す。(b)SubRISC+に実装した異常検出の軽量アルゴリズムの例。用途に応じた参照パターン(異常パターン)をあらかじめ保持し、(a)のようなセンシングデータと比較して類似度dを計算することで、異常をリアルタイムに検出できる。類似度dの値が一定の値以下であれば、センシングデータと参照パターンは十分似通っており、異常であると判定できる。

本研究ではソフトウェアの一例として、加速度データからてんかんの発作をリアルタイムに検出可能な軽量アルゴリズム(図2b)を実装し、実用性を実証した。動作周波数を50 MHzと想定したシミュレーションでは、データのサンプリング速度より高速に異常検出でき、かつ、電力は131.1 µW(マイクロワット)と極めて低い。

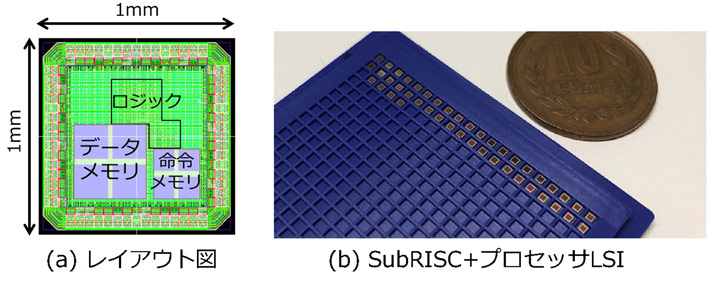

商用で最小の32ビット組み込みプロセッサARM Cortex-M0(表1中央)で同じ処理を行った場合と比べ、1.4倍高速、かつ、電力効率は2.7倍、エネルギー効率は3.8倍であった。本研究ではデータメモリを4 KB、命令メモリを2 KBとしたSubRISC+のプロセッサLSI(図3)を最小の配線半ピッチ(幅)65 nm(ナノメートル)のCMOSプロセスで開発した。

LSIの総サイズは1 mm×1 mm(クレジットカードの厚さが概ね1 mm)と極めて小型である。このプロセッサLSIを5 MHz(ヘルスケアの異常検出ではリアルタイム処理を十分確保できる周波数)で駆動した場合の消費電力は、わずか77.0 µWである。これは、コンビニエンスストア等でも手に入るアルカリボタン電池LR44(主に電卓や万歩計などに使用)で約100日連続稼働できる試算であり、極めて電力効率が高い。

図3. 小型・省電力プロセッサSubRISC+

今回開発したSubRISC+試作チップは65 nmのCMOSプロセスの場合、1 mm×1 mmと小型であり、かつ、わずか77.0 µWの消費電力で、異常検出やデータ探索をリアルタイムに行うことが可能になった。今後はプロトタイプのサンプル配布や展示会出展を検討しているほか、IoTセキュリティ向けにSubRISC+プロセッサをさらに拡張し、より幅広い応用展開を可能にするチップの試作と実用化を目指す。

研究支援

本研究は科学技術振興機構(JST)戦略的創造研究推進事業 ACT-IおよびACT-I加速 研究領域「情報と未来」(研究総括:後藤真孝 産業技術総合研究所 人間情報インタラクション研究部門 首席研究員)における研究課題「大量ストリームデータのリアルタイム処理に向けた柔軟なアーキテクチャ探索と設計環境構築」(研究者:原祐子 東京工業大学 工学院 准教授)の支援を受けて行われた。また、IoTセキュリティ応用を目指した研究開発では、JST 戦略的創造研究推進事業 AIPネットワークラボにおけるAIP加速課題「小型IoTエッジデバイスの軽量暗号アーキテクチャ設計」(研究代表者:原祐子)の支援を受けている。

用語説明

[用語1] プロセッサ : CPU(中央演算処理装置)ともいわれる、コンピュータに内蔵されたパーツ。多くの半導体素子やトランジスタが集まって構築され、コンピュータの中で頭脳の役割を担い、マウスやキーボード、ハードディスク、メモリなどの周辺機器はCPUへデータを送り、制御や演算と呼ばれる動作によりスムーズにパソコンを動かす仕組み。つまりCPUはコンピュータ内にある各機器をコントロールしたり、メモリ上にあるデータを読み書きしたりする機能を行っており、コンピュータ内で命令を出すポジションである。

[用語2] エッジ端末 : エッジとは「データの収集、活用における端の部分」、データの発生源および活用の場に近いところという意味。それぞれの現場に情報処理端末を設置し、その場ごとに“自律分散型”で情報処理を行う仕組みを意味する。

[用語3] CMOSプロセス : Complementary Metal Oxide Semiconductorの略。メモリやマイクロプロセッサはCMOSで作製される。低消費電力であり、最も汎用に用いられている半導体技術である。

[用語4] クラウドコンピューティング : ネットワークに接続されたデバイスで得られたデータをデータセンタやサーバなどに送信し、そこにある高性能計算機を利用して計算した結果を再びデバイスに返す形式のシステムを指す。現在のIoTで多く用いられる形式であるが、エッジ端末の増加に伴いネットワーク帯域を切迫することが考えられ、エッジ端末が処理結果を受信するまでの時間(レイテンシ)が長くなる恐れがある。

[用語5] エッジコンピューティング : クラウドコンピューティングと相反して、エッジ端末やその近くの小型サーバ上でデータを処理する分散システムを指す。データを遠く離れたデータセンタなどに送信する必要がなく、リアルタイム処理を可能にすると期待されている。

[用語6] 組み込みシステム : デスクトップパソコンやノートパソコンのような汎用的な計算機器と異なり、特定の機能(設計時に予め決められた機能)を実現するために組み込まれた専用計算機を指す。組み込みシステムを対象としたプロセッサは、計算資源やメモリの制約が極めて厳しい。

[用語7] RISCプロセッサ : プロセッサにはCISC(Complex Instruction Set Computer)とRISC(Reduced Instruction Set Computer)に大別される。CISCは1回の計算で多数の複雑な処理を行うことで高速化を目指すのに対し、RISCは命令の種類を減らし1回の計算を単純化することで高速化を目指す。商用プロセッサでは、IntelはCISC、ARMはRISCをそれぞれ採用している。

[用語8] 軽量アルゴリズム : 多くのアルゴリズム(計算の手順)には剰余算やそれらを組み合わせた複雑な算術演算を多用している。一方、これらの演算を使用しない、比較的シンプルな演算のみで処理するアルゴリズムは軽量であり、計算資源制約の厳しいデバイスでも効率的に処理することができる。

[用語9] チューリング完全 : 計算機があらゆる処理を実行できる計算能力を備えている場合、その計算機はチューリング完全であると言う。プロセッサは汎用的なソフトウェアを対象にしており、チューリング完全である。

論文情報

本成果は、下記論文にて発表したプロセッサの提案、シミュレーション評価手法を用い、新たに実機を試作、評価したものである。

掲載誌 : |

IEEE Access |

論文タイトル : |

Implementation of Lightweight eHealth Applications on a Low-Power Embedded Processor |

著者 : |

Mingyu Yang(東工大 博士後期課程学生)、原祐子(東工大 准教授) |

DOI : |

お問い合わせ先

東京工業大学 工学院 情報通信系

准教授 原祐子

E-mail : hara@cad.ict.e.titech.ac.jp

Tel / Fax : 03-5734-2914

JST事業に関すること

科学技術振興機構 戦略研究推進部 ICTグループ

舘澤博子

E-mail : rp-info@jst.go.jp

Tel : 03-3512-3525 / Fax : 03-3222-2066

取材申し込み先

東京工業大学 総務部 広報課

E-mail : media@jim.titech.ac.jp

Tel : 03-5734-2975 / Fax : 03-5734-3661

科学技術振興機構 広報課

E-mail : jstkoho@jst.go.jp

Tel : 03-5214-8404 / Fax : 03-5214-8432