東工大ニュース

東工大ニュース

公開日:2014.02.19

東京工業大学大学院理工学研究科の松澤昭教授と岡田健一准教授らの研究グループは、ディジタル回路で構成する新方式のクロック生成回路の作製に成功した。発振器が注入信号に同期して発振をおこす「注入同期現象」を安定的に利用し、フィードフォワード制御による位相同期を行うことにより実現した。従来のクロック生成回路は、帰還(フィードバック)制御による正確な位相同期が必要なため、ディジタル回路では構成できなかった最小加工寸法65nm(ナノメートル)のシリコンCMOS プロセスで試作した新型クロック発生回路は、0.4G~1.4GHz(ギガヘルツ、1GHz は10 億ヘルツ)のクロックを生成可能であり、0.9GHz 出力時の消費電力は0.78mW と非常に低い。0.0066mm2 の極小寸法で実現した。クロック生成回路は、ほぼすべての集積回路に内蔵されており、新方式のクロック生成回路を使えば、身のまわりのあらゆる機器に超小型バッテリーレスセンサーを組み込むことが可能となる。

この成果は9日からサンフランシスコで開かれる「ISSCC (国際固体回路国際会議)」で11日に発表する。

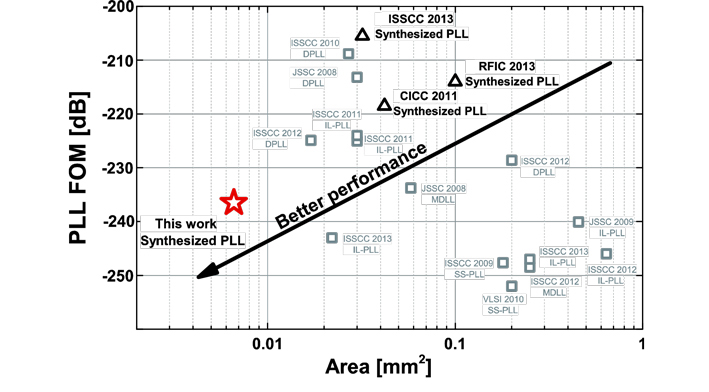

特徴: 国際会議で報告された最新の研究成果との比較において、大幅な小型化・低ジッタ化を実現した。灰色字のものは手設計によるPLLで、黒字のものは自動設計PLLである。星形の本成果によるPLLは、自動設計が可能で且つディジタル回路のみで構成できるため、大幅な小型化および低消費電力化を実現している。

お問い合わせ先

大学院理工学研究科電子物理工学専攻 岡田健一

Tel: 03-5734-2258 Fax: 03-5734-3764

Email: okada@ssc.pe.titech.ac.jp