東工大ニュース

東工大ニュース

公開日:2014.06.09

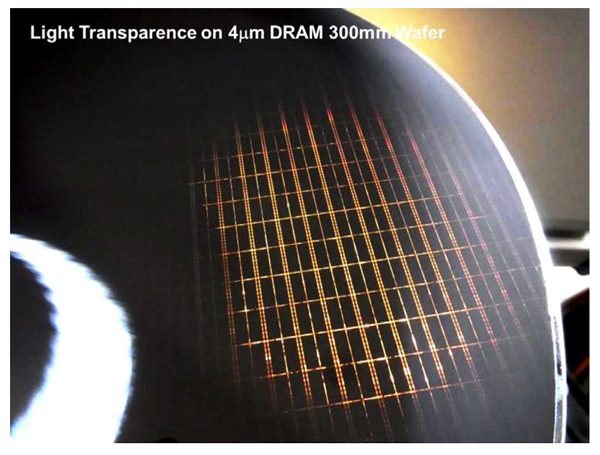

東京工業大学異種機能集積研究センターの大場隆之特任教授は、ディスコ、富士通研究所、PEZY Computing(ペジーコンピューティング、東京都千代田区)、WOWアライアンス(用語1)と共同で、半導体メモリー(DRAM)が搭載された直径300mmシリコンウエハー(基板)の厚さを4マイクロメートル(µm)まで超薄化する技術を開発した。同技術はバンプ(用語2)を用いないWOW積層技術(用語3)を利用して、シリコンウエハーの厚さをデバイス層より薄い4µmまで薄化することに成功したものである。

薄化前と薄化した後のリフレッシュ時間の累積故障率が変わらないことを確認し、薄化による新たな原子欠陥が生じないことを実証した。この薄化プロセスを用いれば、上下積層チップの配線長が従来の1/10以下になり、配線抵抗と配線容量が大幅に低減される。超小型でテラビット(1テラは1兆)級の大規模メモリーへの応用が期待される。

この成果は米国ハワイで6月10~13日に開かれる国際電子デバイス会議「VLSIシンポジウム2014」で発表する。

1. WOWアライアンス: |

東京工業大学を中心に設計・プロセス・装置・材料半導体関連の複数企業および研究機関からなる研究グループ。薄化したウエハーを簡単に積層することができ、バンプレスTSV配線を用いた三次元化技術を世界で初めて開発に成功した。 |

2. バンプ: |

電極部にメッキで形成した配線接続のための突起。 |

3. WOW積層技術 : |

ウエハーの積層(Wafer-on-Wafer)で大規模集積回路を作製する三次元集積技術。積層方法には、チップ同士の積層(Chip-on-Chip)、チップとウエハーの積層(Chip-on-Wafer)があり、COC、COW、WOWの順に生産性が高くなる。 |

学会名: |

IEEE 2014 Symposia on VLSI Technology and Circuits |

題名: |

Ultra Thinning Down to 4-µm using 300-mm Wafer40-nm Node 2Gb DRAM for 3D Multi-Stack WOW Applications |

発表者: |

Y.S. Kim, S. Kodama, Y. Mizushima, N. Maeda, H. Kitada, K. Fujimoto, T. Nakamura, D. Suzuki, A. Kawai, K. Arai and T. Ohba |

図: 4µm まで薄化した 300mm DRAM ウエハー。このような薄いウエハーになると可視光が透過する。

お問い合わせ先

東京工業大学異種機能集積研究センター

秘書 沼澤文恵

Tel: 045-924-5866

Email: numazawa.f.aa@m.titech.ac.jp

東京工業大学 広報センター

Tel: 03-5734-2975

Email: media@jim.titech.ac.jp