東工大ニュース

東工大ニュース

公開日:2023.04.26

東京工業大学 科学技術創成研究院 未来産業技術研究所の菅原聡准教授と工学院 電気電子系の塩津勇作博士後期課程大学院生(研究当時)らは、エネルギー最小点(EMP)[用語1]動作によって動作時電力を99%削減し、また、パワーゲーティング(PG)によって重みデータを失うことなく待機時電力を84%削減できる、プロセッシング・イン・メモリ(PIM)型のニューラルネットワーク(NN)アクセラレータ[用語2]のマクロ[用語3]を開発した。本技術はCMOSのみで構成できる。このPIM型マクロのメモリ部にはEMPで動作し、超低電圧リテンション(ULVR)によるPGが可能な新しいSRAM技術を用いた(ULVR-SRAM[用語4])。ULVR-SRAMの導入によって可能となるEMP動作を用いることで推論のエネルギー効率(TOPS/W[用語5])は大幅に向上し、また、許容される積和(MAC)演算の並列数も大幅に増やすことができることから、演算能力(TOPS)も大きく向上できる。本マクロを用いてMAC演算の適切な並列化を行いEMP動作させることで、通常電圧動作時や従来技術に比べて、演算能力が同じであれば、1/10程度の消費電力で済み、また、消費電力が同じであれば、10倍程度の演算能力を実現できる。全結合層を用いたベンチマークから、このEMPによる推論では、65 TOPS/Wもの高いエネルギー効率を示した。本技術は将来のスマート社会で重要となるモバイルエッジ[用語6]デバイスに搭載可能な低消費電力・高性能AIアクセラレータ技術となる。

本成果はIEEE(米国電気電子学会)の「IEEE Journal on Exploratory Solid-State Computational Devices and Circuits」誌に12月22日付けで掲載された。

将来のスマート社会では、スマートフォンなどのスマートモバイルエッジ階層のコンピューティングシステムにAI技術を導入することが期待されており、これまで以上に動作時電力および待機時電力がともに低く、エネルギー効率の高いニューラルネットワーク(NN)アクセラレータが要求されている。NNアクセラレータには様々な構成方法があるが、processing-in-memory(PIM)型のハードウェアは、メモリアレイの中または近傍に演算ユニットを配置することで、バスを介したデータ転送を用いることなく、データの処理が可能なことから、NNアクセラレータの高性能化に有効である。特に、SRAMを用いたPIM型NNアクセラレータは現状のCMOS技術で実装が可能なため、応用上極めて重要である。

NNアクセラレータのエネルギー効率を向上させるためには、エネルギー最小点(EMP)となる駆動電圧(VEMP)を用いた推論動作が極めて効果的になる。EMP動作には許容される積和(MAC)演算の並列数を増大させ、演算能力を向上させるという効果もある。また、モバイルエッジ応用ではパワーゲーティング(PG)による待機時電力の削減も必須であるが、従来の6TセルをSRAMに用いた場合、EMP動作およびPGを実現することはできない。特殊なセル構成を用いてEMP動作またはPGのいずれかを実現できても、2つを同時に実装した例はない。

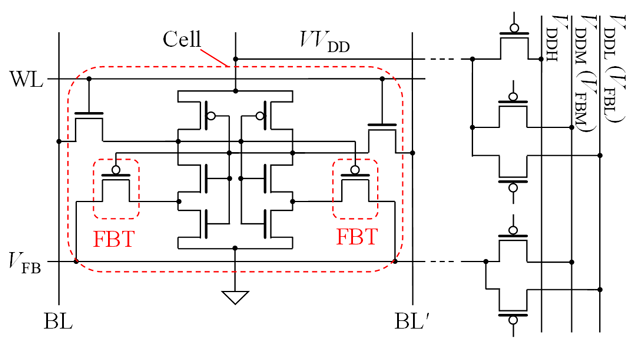

最近、本研究グループは、通常電圧下(VDD)では従来のSRAMと同様の高性能SRAM動作を実現し、0.2 V程度の超低電圧(VUL)でもデータを失うことなく保持できる超低電圧リテンションSRAM(ULVR-SRAM)セルを提案した(図1)。ULVR-SRAMでは、VULでデータ保持(ULVR)を行うことで実質的なPGを実現できるため、SRAMであっても待機時電力の大幅な削減が可能となる。さらに、ULVR-SRAMでは、このセルの特徴からEMP動作も実現できる可能性がある。すなわち、電源電圧をEMPとなる電圧VEMPまで低減させてSRAM動作させることで、エネルギー効率を最大化できると考えられる。

したがって、PIMのSRAM部にULVR-SRAMを用いることで、PGとEMP動作が可能なNNアクセラレータを実現できると考えられ、従来のSRAM技術では到達できない高いエネルギー効率を実現できる可能性がある。本研究では、EMPで動作し、PGが可能なULVR-SRAM技術を新たに開発し、これを用いたPIM型NNアクセラレータのマクロ技術を開発した。

図1. 提案したULVR-SRAMセルの回路構成

開発したULVR-SRAMは(1)通常電圧VDD(=1.2 V)での高性能SRAM動作、(2)EMPとなる電圧VEMP(=0.4 V)を用いた最大エネルギー効率SRAM動作、(3)超低電圧VUL(=0.2 V)を用いたデータ保持(ULVR)による実質的なPGの3モード動作を実現できる。

本研究では、はじめに、この3モード動作を実現できるULVR-SRAMセルの設計技術の開発を行った。トランジスタの特性バラツキを考慮して、設計指標には各動作モードにおけるノイズマージンと、ULVRモードにおけるリーク電流を用いた。最適設計されたULVR-SRAMセルを用いてPIM型NNアクセラレータ・マクロの設計を行った。今回、NNのアーキテクチャには2値化ニューラルネットワーク(BNN)を用いた(本技術は他の多ビットのNNアーキテクチャにも応用できる)。

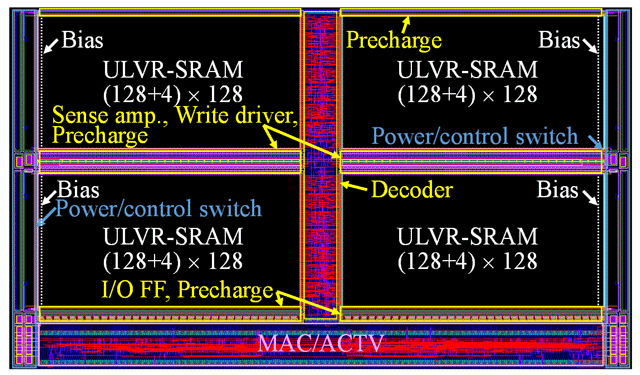

図2に開発したPIM型BNNアクセラレータ(BNA)マクロの構成とレイアウトを示す。このマクロ1つで256 bの入力ベクトルに対する積和演算が可能である。このBNAマクロは重みデータとバイアスデータを格納するためのULVR-SRAMを有し、これらの同時読み出しによって効率的にMAC演算を実行し、アクティベーション判定を行うことができる。

図2. PIM型BNAマクロのレイアウト

開発したBNAマクロのPG性能について調べ、待機電力削減効果を評価した。このBNAマクロのPGではメモリセル部はVUL=0.2 Vでデータ保持を行い、その他の回路は電源遮断を行う。このPGによって、待機時電力を84%削減できる(クロックゲーティング時のスタンバイ状態からの比較)。これは従来の6TセルのSRAMを用いた場合の待機時電力と比較すると94%の削減率となる。

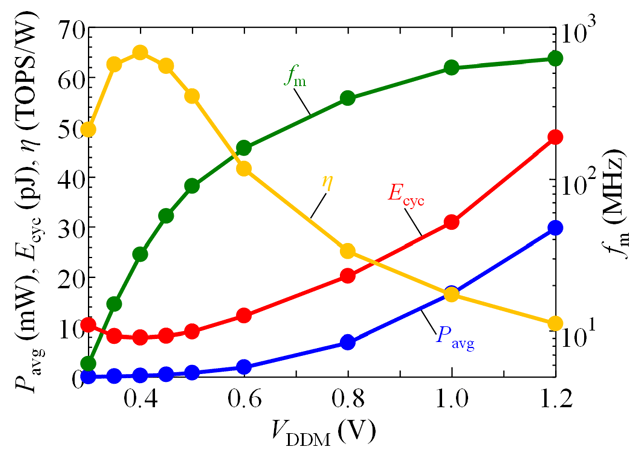

次に、推論動作時の性能評価を行った。図3にBNAマクロにおけるEMP動作の解析結果を示す。電源電圧(図中のVDDM)の減少とともに平均動作時電力(Pavg)と動作周波数(fm)は減少し、0.4 Vで消費エネルギー(Ecyc)が最小となる。すなわち、VEMPは0.4 Vとなる。このVEMPの動作点では通常電圧動作(1.2 V)と比較して動作周波数fmは1/10となるが、動作時電力は大幅に削減され、1/100になる(99%減)。この特徴は後述するMAC演算の並列化に極めて有効となる。また、同図にはBNAにおける推論のエネルギー効率ηも示している。ηはVEMPである0.4 Vで最大となり、65 TOPS/Wと極めて高い値を実現できる。

図3. 消費エネルギーEcyc、平均動作時電力Pavg、動作周波数fm、エネルギー効率ηの電源電圧VDDM依存性

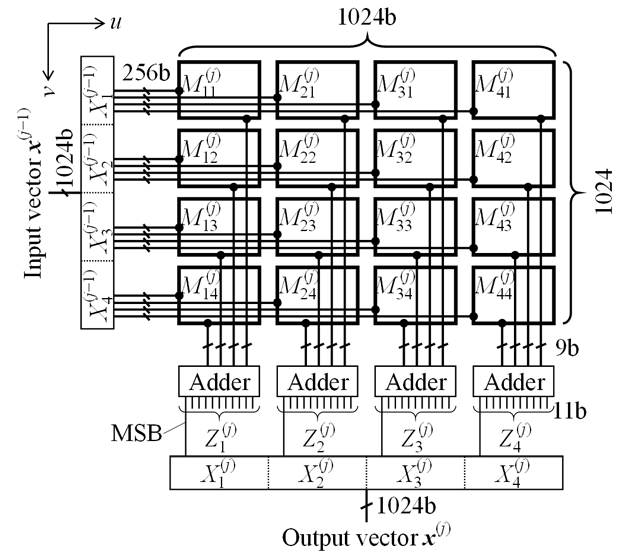

任意のサイズ・形状のネットワークは複数のBNAマクロを用いて構成できる。図4にBNAマクロを用いた1,024ノードの全結合層の構成例を示す。Muv(j)が1つのBNAマクロを表し、この場合では16個のマクロと追加の加算器で容易に全結合層を構成できる。以下、図中のv軸方向にある複数のBNAマクロを同時にMAC演算することをノード内並列化(INP)と呼び、u軸方向にある複数のBNAマクロを同時にMAC演算することをレイヤ内並列化(ILP)と呼ぶ。それぞれの並列化による並列数をNINP、NILPとすれば、全体の並列数NPはNINPとNILPによって与えられる。1つのマクロ当たりMAC演算ユニットを1つ有する場合、NP=16となる。さらに、1マクロ当たりMAC演算ユニットを増やすことで、NPは大きくとれる(開発したBNAマクロではMAC演算ユニットの増設は容易である)。

図4. 開発したBNAマクロを用いた全結合層の構成例

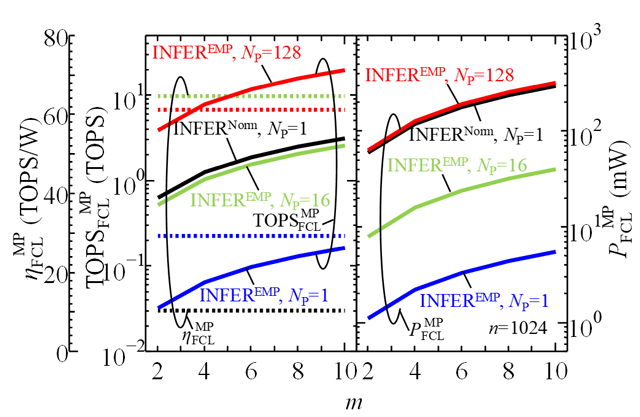

図5に並列化の効果を示す。この図は平均動作時電力(PFCLMP)、演算能力(TOPSFCLMP)、エネルギー効率(ηFCLMP)のネットワーク層数m依存性である。全結合層1層あたりのニューロン数は1,024である。黒線が通常電圧(VDD=1.2 V)における推論モード(INFERNormモード)の場合で総並列数NPを1としたとき、青線、緑線、赤線はそれぞれEMP電圧(VEMP=0.4 V)にける推論モード(INFEREMPモード)でNP=1、16、128とした場合を示している。NP=1の場合に現れているように、EMPによる演算能力の劣化の効果は消費電力の削減率より小さい。したがって、MAC演算の並列化によって高性能化を実現できる。NP=16の場合では、EMP動作を用いることで1.2 V動作時と同程度の演算性能を保ちながら、Pavgを1.2 V動作時の約1/10にできる。また、NP=128にすると(1マクロあたり8並列)、Pavgは1.2 V動作時と同程度であるが、演算量を10倍程度に増大できる。また、EMP動作時の演算効率(ηFCLMP)はどの場合でも概ね65 TOPS/W程度と非常に高い。以上から、ULVR-SRAMをメモリ部に用いたPIM型NNアクセラレータは、待機時電力の削減効果を大きくとれ、また、エネルギー効率に優れ、消費電力の削減および演算能力の高性能化を実現できる。

図5. 全結合層の平均動作時電力PFCLMP、演算能力TOPSFCLMP、エネルギー効率ηFCLMP

将来のスマート社会では、AI技術をクラウドだけでなく、モバイルエッジ階層にまでその応用範囲を拡張することが重要・必要となってくる。モバイルエッジ階層でAI技術を実現できれば、クラウドを介した通信のレイテンシの問題を解消することが可能となり、また、クラウドとの非接続状態でも使用できる。モバイルエッジ階層への応用では、演算能力とエネルギー効率が高く、低消費電力なAIシステムが必要不可欠となり、このためには、これまで以上に高性能なアクセラレータが要求される。本技術は、新しいSRAM技術(ULVR-SRAM)を用いて構成したPIM型NNアクセラレータのマクロ技術であり、以下のような特徴を持つ:(i)モバイルエッジ応用に必須の低消費電力化と高性能化を実現できる、(ii)マクロで構成されているため、回路設計者が目的に合わせて任意のサイズ・形態のNNを構成できる、(iii)CMOSコンパチブルな技術である。したがって、モバイルエッジデバイスへの搭載も可能であり、将来のスマート社会におけるAI技術の1つの担い手となる可能性がある。

本研究で採用したPIM型ハードウェアはメモリアレイの中もしくは近傍にMACユニットを配置することで、メモリアレイから取り出したデータを、バスを介したデータ転送を用いることなく直接処理することができる。PIMハードウェアのこの特徴は消費電力の低減に有効なだけでなく、バスによる制約を受けることなくMAC演算を効率的に並列化できることから、演算能力の向上にも極めて有用である。これらの効果に加えて、本研究でPIMに導入を行ったULVR-SRAMは、従来のSRAMでは実現が困難なPG とEMP動作の両方を実現できる。したがって、ULVR-SRAMを用いて構成したPIM型NNアクセラレータはモバイルエッジのAI技術として要求される動作時・待機時消費電力を低く抑え、演算能力・エネルギー効率の高いアクセラレータ技術となる。今後は、本マクロ技術をたたみ込み層などにも応用していく。簡単な解析からは本技術をたたみ込み層に応用することで200 TOPS/W以上の高いエネルギー効率が得られることがわかっている。また、ユーザーフレンドリなマクロベースの設計技術を確立していく。

用語説明

[用語1] エネルギー最小点(EMP) : CMOSロジックシステムで消費される全エネルギーは回路動作に基づく動作時エネルギーと、トランジスタのリークによって生じる待機時エネルギーからなる。これらはそれぞれ異なる電圧依存性を有することから、全エネルギーは特定の電圧で最小値をとる。この全エネルギーが最小となる動作点がEMPである。EMPを動作電圧とすることで、エネルギー効率を最大化できる。

[用語2] アクセラレータ : 特定の処理を高速化できるハードウェアまたは演算システム。特に、AIシステムでは、各種ニューラルネットワーク(NN)の推論処理に特化した専用のアクセラレータが用いられることも多い。AI半導体の分野では、NNアクセラレータやAIアクセラレータとも呼ばれる。

[用語3] マクロ : 特定の機能を持つ回路ブロック。例えば、SRAMでは比較的小さな記憶容量(数kB程度)のマクロを作っておき、これを複数個組み合わせることで任意のサイズのメモリを実現できる。

[用語4] ULVR-SRAM : 超低電圧でデータ保持(リテンション)できるSRAMのことで、本研究者らによって提案された。動作モードの切り替えが可能な特殊なインバータを用いて構成され、通常の電圧では従来のSRAMと同等の高性能SRAM動作を実現し、0.2 V程度の超低電圧では、記憶データを失うことなくリテンションを行い、待機時電力を大幅に削減できる。この超低電圧リテンションに用いる動作モードを応用することでエネルギー最小点(EMP)でのSRAM動作が可能となる。詳細は以下の論文を参照:H. Yoshida, Y. Shiotsu, D. Kitagata, S. Yamamoto, and S. Sugahara, IEEE Open J. Circuits Syst., 2, pp. 520-533 (2021).

[用語5] TOPS、TOPS/W : TOPSはtera operation per secondの略で、1秒当たりの演算数を意味する。TOPS/WはTOPSを電力で割った指標で、エネルギー当たりの演算数に相当し、エネルギー効率を表す。これらの指標はNNアクセラレータの性能評価の指標として用いられる。

[用語6] モバイルエッジ : 将来のスマート社会におけるコンピューティングシステムは、クラウド、エッジ、モバイルエッジ、ウェアラブルといった階層から構成されると予想されている。モバイルエッジはスマートフォンなどのスマートモバイルデバイスを中心とするコンピューティング階層で、モバイル環境下におけるコンピューティングの中心的な役割を担う。

論文情報

掲載誌 : |

IEEE Journal on Exploratory Solid-State Computational Devices and Circuits |

論文タイトル : |

Binarized Neural Network Accelerator Macro Using Ultralow-Voltage Retention SRAM for Energy Minimum-Point Operation |

著者 : |

Yusaku Shiotsu, and Satoshi Sugahara |

DOI : |

お問い合わせ先

東京工業大学 科学技術創成研究院 未来産業技術研究所

准教授 菅原聡

Email sugahara@isl.titech.ac.jp

Tel / Fax 045-924-5456

東京工業大学 科学技術創成研究院 未来産業技術研究所

博士研究員 塩津勇作

Email y.shiotsu@isl.titech.ac.jp

Tel / Fax 045-924-5456

取材申し込み先

東京工業大学 総務部 広報課

Email media@jim.titech.ac.jp

Tel 03-5734-2975 / Fax 03-5734-3661