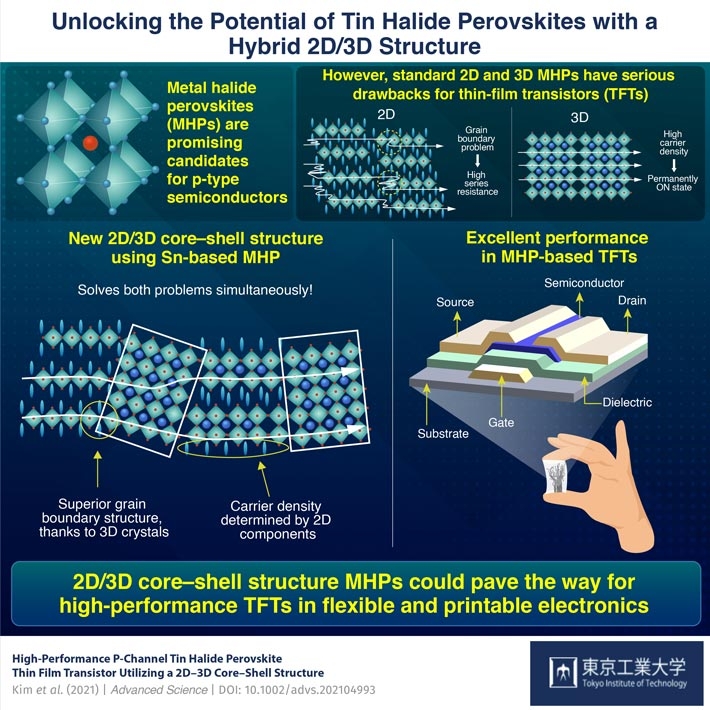

Metal halide perovskites (MHPs) are a class of materials with promising properties for semiconductor applications, such as thin-film transistors (TFTs). In particular, tin (Sn)-based MHPs could be an environmentally benign alternative to lead-based ones, which are toxic. However, some critical issues need to be resolved before Sn-based MHPs can be leveraged in planar semiconductor devices.

When arranged into a 2D structure (or quasi-2D structure with a few layers), defects in the crystal structure of Sn-based MHPs called "grain boundaries" hamper the mobility of charge carriers throughout the material. If used in a TFT, this phenomenon results in a large series resistance that ultimately degrades performance. In contrast, a TFT made using an Sn-based MHP arranged into a 3D structure faces a different yet still crippling problem. The extremely high carrier density of the 3D material causes the transistor to be permanently ON unless very high voltages are applied. Needless to say, this renders such a device useless for many applications.

Fortunately, a team of scientists from Tokyo Tech, Japan, have found a solution to these limitations. In a recent study published in Advanced Science and led by Assistant Professor Junghwan Kim and Honorary Professor Hideo Hosono, the researchers proposed a novel concept based on a hybrid structure for Sn-based MHPs, called the "2D/3D core–shell structure." In this structure, 3D MHP cores are fully isolated from one another and connected only through short 2D MHP strips (or "shells"). This alternating arrangement solves both of the abovementioned drawbacks simultaneously. But how?

The trick to lowering the series resistance of 2D MHPs is to eliminate the carrier mobility problems at grain boundaries, which are caused by misalignments between the conductive octahedra of the perovskite. Thanks to the way in which the 3D cores connect to the 2D segments, these misalignments disappear and the series resistance is greatly lowered. As for the high carrier density of 3D MHPs, this problem is simply not present when using the 2D/3D core–shell structure. Since the 3D cores are isolated, their carrier density is no longer relevant; instead, the 2D segments act as a bottleneck and limit the effective carrier density of the overall material.

To demonstrate the effectiveness of this novel structure, the team fabricated a complementary metal–oxide–semiconductor (CMOS) inverter by combining 2D/3D TFTs with a standard indium gallium zinc oxide TFT. "Our device exhibited a high voltage gain of 200 V/V at a drain voltage of 20 V. This performance is the best reported so far for a CMOS inverter made using Sn-MHP TFTs," highlights Prof. Kim.

The innovative 2D/3D structure presented in this study will help scientists worldwide take advantage of the attractive electronic properties of perovskites. Moreover, their approach is not limited to a narrow class of materials or device types. "The proposed strategy could be applied to various solution-derived semiconductor systems, opening doors to flexible and printable electronics," says Prof. Kim.

Only time will tell what technological innovations are unlocked by the findings of this study!

. Any information published on this site will be valid in relation to Science Tokyo.