東工大ニュース

東工大ニュース

公開日:2021.06.22

東京工業大学 科学技術創成研究院 異種機能集積研究ユニットの大場隆之特任教授は、WOWアライアンス[用語1]との共同研究により、低消費電力・超小型の電源基板「キャパシタ[用語2]内蔵Siインターポーザ[用語3]」の開発に成功した。手法として、バンプ[用語4]を使わないウエハレベルのパッケージ化プロセスであるバンプレスChip-on-Wafer(COW)[用語5]を創出した。

現在、2次元での微細化による半導体デバイスの高性能化に限界が見られるなか、さらなる高性能化・低消費電力化を目指した3次元積層半導体の開発が進められている。しかし、3次元積層による半導体のパッケージ化では、蓄電装置であるキャパシタと半導体の間の配線が長くなり、伝達スピード低下の一因となる寄生容量[用語6]も大きくなるという問題があった。

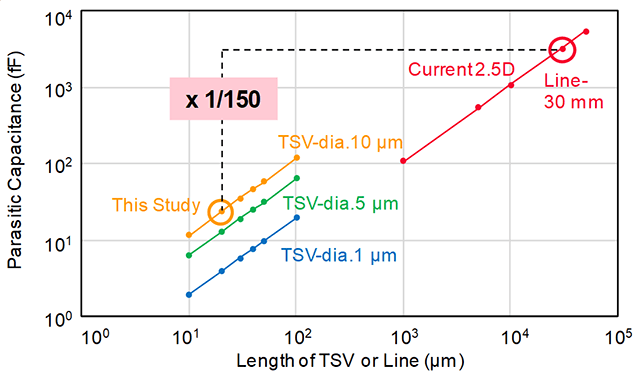

本研究では、銅(Cu)を配線に用い、埋め込み・研磨によって垂直配線を行うCuダマシンTSV[用語7]配線を用いながら、半導体とパッケージ基板をつなぐSiインターポーザにキャパシタを内蔵することで、半導体とキャパシタの間の配線長を従来に比べて1/100に短縮することに成功した。その結果、従来に比べて寄生容量は1/150になり、低消費電力につながることが明らかになった。

この成果はバーチャルカンファレンスとして6月1日(火) ~ 7月4日(日)に開催される半導体パッケージング技術に関する国際会議「ECTC2021」(主催:IEEE)で発表された。

パソコンやスマートフォンのCPU、また電化製品のセンサー、制御装置などに欠かせない半導体は、これまで微細化によって性能を向上させてきた。ところが、2次元的な微細化という従来の手法の延長線上にある技術では、これ以上の性能向上は難しいという物理的な限界が迫っている。

こうした2次元的な微細化の限界を突破し、半導体デバイスのさらなる高性能化、低消費電力化を実現するために、回路素子を配置したウエハをミクロンレベルまで薄くし、TSV配線を用いて立体的に重ねる3次元積層の開発が急ピッチで進められている。

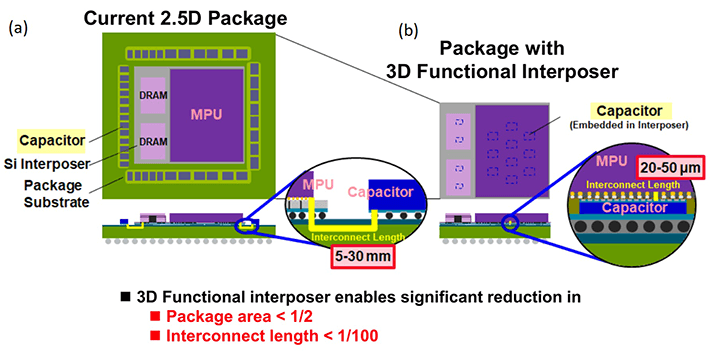

従来の3次元積層による半導体パッケージでは、キャパシタ(capacitor)は接合用のバンプを使ってサブストレート(package substrate)[用語8]にはんだ付けされるので、半導体(MPU、DRAM)とキャパシタの間の配線長(interconnect length)が5 mm~30 mmと長くなり、寄生容量が大きくなってしまうという問題があった(図1a)。さらに、数多くのキャパシタを半導体の周囲に配置するため、パッケージの寸法が半導体の寸法よりも大きくなってしまうという点も問題だった。

本研究では、抵抗率の低い銅配線を用いた伝送路であるCuインターコネクトを採用しながら、Siインターポーザにキャパシタを内蔵できるバンプレスChip-on-Wafer(COW)プロセスを開発し、半導体とキャパシタの間の配線長を従来に比べて1/100に短縮することによって、超小型、かつ、低消費電力な電源基板を実現することを目指した(図1b)。

図1. 半導体パッケージ構造

(a)現状2.5Dパッケージ、(b)開発した電源基板を用いた3Dパッケージ

(a)現状2.5Dパッケージ、(b)開発した電源基板を用いた3Dパッケージ

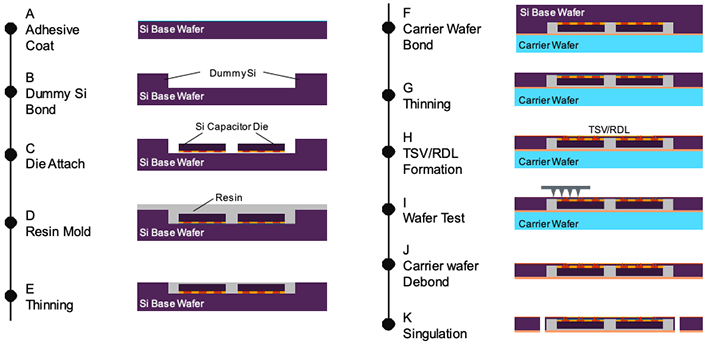

本研究では、キャパシタをSiインターポーザに内蔵する方法として、バンプレスChip-on-Wafer(COW)プロセスを開発した(図2)。以下、図に沿ってその流れを説明する。

まず、直径300 mmの Siベースウエハに、接着剤(adhesive)を5 µmの厚さで塗布する(図2-A)。その接着剤の上にキャパシタを搭載し、接着剤を硬化させることで、Siベースウエハとキャパシタとを接着させる(図2-B、C)。次に、エポキシ樹脂(resin)でSiベースウエハ全体を低圧でコンプレッション(モールド)成形して(図2-D)、その樹脂を薄化(thinning)する(図2-E)。

続いて、その後のCOWプロセス中のウエハ反りを最小化するため、ベースウエハを裏返し、薄化した樹脂側に、強化材として厚さ300 mmの Siキャリアウエハを接合する(図2-F)。その上で、ベースウエハの厚みを775 µmから20 µmまで薄化(図2-G)。さらにTSVとRDL[用語9]を形成することで、キャパシタとRDLを接続させる(図2-H)。今回の研究では、このキャパシタとRDLの接続後にウエハテストを行い、電源基板の電気特性を評価した(図2-I)。

実装する際は、Siキャリアウエハを除去し(図2-J)、切り離しを行った(図2-K)ものを使用する。

図2. バンプレスCOWプロセスフロー

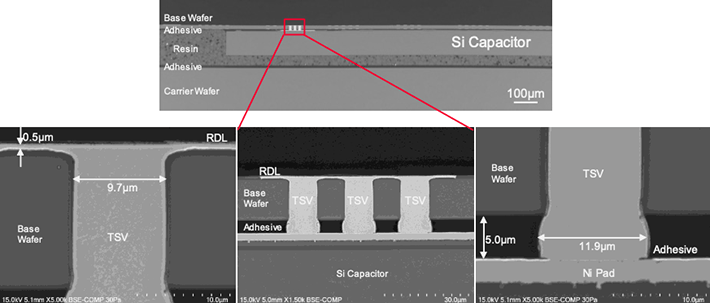

このバンプレスChip-on-Wafer(COW)プロセスによって作製した、電源基板におけるTSVとキャパシタ端子の接続部の断面を観察した。その結果、クラックや剥離などの欠陥はなく、また特にTSVとキャパシタ端子の間にも酸化膜残渣などは確認されず、良好な接続が得られていることが分かった(図3)。

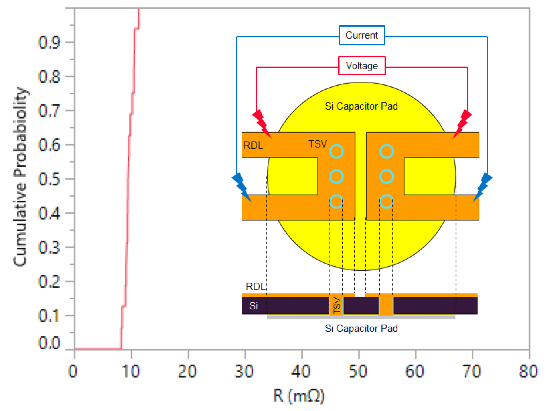

電源基板の電気特性として、TSVの接続抵抗(R)を測定したところ、10mΩで極めて安定していた(図4)。これはSiインターポーザに内蔵されたキャパシタに反りや収縮がほとんど発生していないことを意味している。この評価によって得られたTSV接続抵抗を前提として、今回開発した電源基板を使った場合の配線長の短縮による寄生容量(parasitic capacitance)の低減効果を計算したところ、寄生容量が従来に比べて1/150に小さくなるという数値が算出された(図5)。

図3. キャパシタを内蔵した電源基板の断面写真

図4. TSVの接続抵抗

図5. 配線長の短縮による寄生容量の低減効果

今回開発された電源基板「キャパシタ内蔵Siインターポーザ」は、3次元積層半導体のパッケージに用いることで、半導体パッケージの低消費電力化、超小型化に貢献することが期待される。

今後は、このキャパシタ内蔵Siインターポーザと3次元積層半導体をバンプレスTSV配線による3次元化技術で直接接続することによって、半導体パッケージの低消費電力化、超小型化の実証を目指す。

用語説明

[用語1] WOWアライアンス : 東京工業大学を中心とした産学研究プラットフォーム。半導体関連の設計・プロセス・装置・材料などを手がける企業、および研究機関によって構成される。高度かつ簡便なウエハの薄化技術・積層技術を持ち、バンプレスTSV配線を用いた3次元化技術を世界で初めて開発に成功した。

[用語2] キャパシタ : 電気二重層の現象の原理が応用された蓄電装置。電源回路などに用いられる。従来のコンデンサよりも充電効率が高い。

[用語3] Siインターポーザ : 半導体のパッケージにおいて、端子ピッチが異なる半導体とパッケージ基板の間を中継するSi製の電源基板。主に、ハイエンド向け半導体のパッケージにおいて用いられる。

[用語4] バンプ : 電極部にメッキで形成した配線接続のための突起。

[用語5] Chip-on-Wafer(COW) : チップをウエハ上に接合する技術。一般的にチップの接合は、樹脂材料でできた配線基板に対して行われており、それと区別するために「ウエハ上に(Chip-on-Wafer)」という表現が用いられている。チップをウエハ上に接合することにより、以降の半導体製造工程において、各種装置を用いた高精度な加工が行えるようになる。

[用語6] 寄生容量 : 電圧のかかった導体の間に、設計の意図から外れて発生する電気的な負荷。

[用語7] TSV(Through-Silicon-Via) : シリコン(Silicon)ウエハを貫通(Through)させて開けた接続孔(Via:ビア)。上下に積層したチップを、埋め込み配線によって接続させる。最近では、シリコン材料以外にも配線するため、前工程における垂直配線(vertical interconnects)とした方が分かりやすい。

[用語8] サブストレート(Package Substrate) : Substrateを和訳すると「回路基板」だが、一般的な配線基板(プリント基板)に対して、半導体パッケージの基板を指すために使われる。

[用語9] RDL(Re-Distribution-Layer) : 半導体やキャパシタなどの部品の端子からTSVなどの上下貫通ビアを介して引き出す配線。

学会発表

学会名 : |

IEEE 71st Electronic Components and Technology Conference (ECTC2021) |

論文タイトル : |

Miniaturized 3D Functional Interposer Using Bumpless Chip-on-Wafer (COW) Integration with Capacitors |

発表者 : |

Tatsuya Funaki, Yoshiaki Satake, Kyosuke Kobinata, Chih-Cheng Hsiao, Hitoshi Matsuno, Shunsuke Abe, Youngsuk Kim, and Takayuki Ohba |

お問い合わせ先

研究に関すること

東京工業大学 科学技術創成研究院 異種機能集積研究ユニット

秘書 沼澤文恵

E-mail : numazawa.f.aa@m.titech.ac.jp

Tel : 045-924-5866

取材申し込み先

東京工業大学 総務部 広報課

E-mail : media@jim.titech.ac.jp

Tel : 03-5734-2975 / Fax : 03-5734-3661