東工大ニュース

東工大ニュース

公開日:2020.06.22

東京工業大学 科学技術創成研究院 異種機能集積研究ユニットの大場隆之特任教授は、WOWアライアンス[用語1]と共同で、ステルスダイシング[用語2]と呼ばれるレーザーダイシング加工プロセスを用いた、ダメージが生じない極薄ウエハ加工技術の開発に成功した。

現在、2次元半導体デバイスの微細化の限界を突破し、高性能化・低消費電力化を目指して、極薄ウエハを使った3次元積層半導体の開発が進められている。しかし極端に薄いウエハを分割すると欠けが増加するという問題があった。本研究では、レーザーダメージ評価用に微細配線を有するTEG[用語3]ウエハを開発し、ダメージ量とその発生位置の定量化に成功した。さらに今回開発したダイシング手法では、ダイシングストリート幅[用語4]を従来技術に比べて1/4に縮小できるため、チップ収率の向上にもつながることが分かった。

この成果はバーチャルカンファレンスとして6月3日(水) ~ 30日(火)に開催される半導体パッケージング技術に関する国際会議「ECTC2020」(主催: IEEE)で発表する。

パソコンやスマートフォンに欠かせないCPUやメモリなどの半導体は、微細化により性能を向上させてきた。ところが、従来技術の延長線上ではこれ以上微細化できないという物理的な限界が迫っている。こうした2次元的な微細化限界を突破し、半導体デバイスのさらなる高性能化、低消費電力化を実現するために、ウエハをミクロンレベルまで薄くし、TSV[用語5]配線を用いた3次元積層の開発が急ピッチで進められている。

しかし、ウエハを元の厚さから1/10以下まで薄くしこれをダイシング(分割)すると、チッピングと呼ばれる欠けが増加する。またダイシングストリート幅によってウエハ当たりのチップの数が決まるため、チッピングがなく、ダイシングストリート幅ができるだけ狭いダイシング方法が必要とされる。このため、ステルスダイシング(SD)と呼ばれるレーザーダイシング技術がすでに実用化されている。

本研究では、デバイス面に生じるわずかなダメージの評価方法を確立すること、そしてステルスダイシングにおけるレーザー波長と照射方法を工夫することによって、ダイシングストリート幅を従来技術よりも縮小することを目指した。

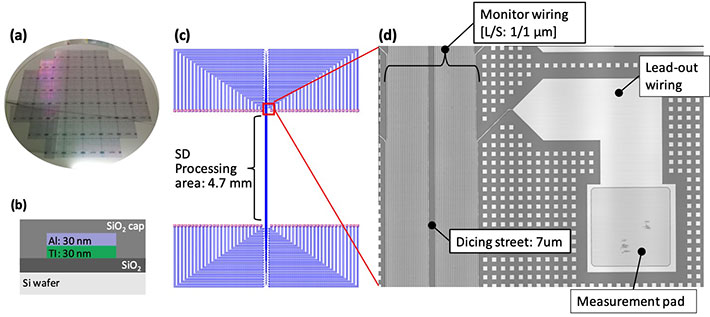

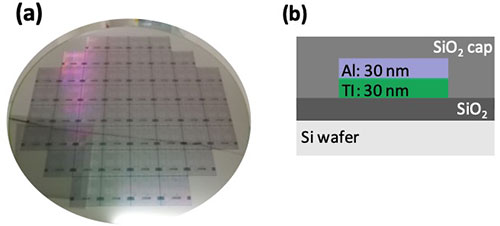

本研究では、ダメージ検出のための評価用チップとして、配線幅/スペースが1 µm/1 µm(Al/Ti)のTEGウエハを開発した(図1a)。このウエハでは、ダメージ感度を向上させるためにAlとTiの膜厚をそれぞれ30 nmとした(図1b)。ダメージ発生位置を検出するためのモニタリング配線は、レーザー加工ライン(ダイシングストリート)に対して平行に1 µmピッチで設計されている(図1c, d)。レーザー加工後に、測定パッドを通して各モニタリング配線の抵抗値変化率を計算することでダメージを評価した。

図1. TEG構造:(a)TEGウエハ、(b)配線構造、(c)配線の拡大図、(d)配線の断面構造図

図1. TEG構造:(a)TEGウエハ、(b)配線構造、(c)配線の拡大図、(d)配線の断面構造図

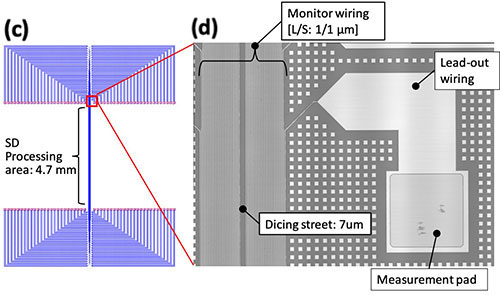

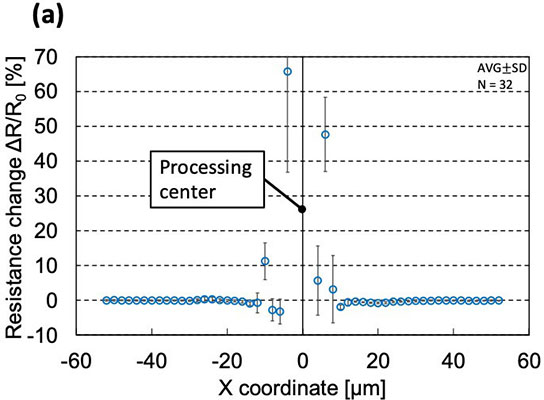

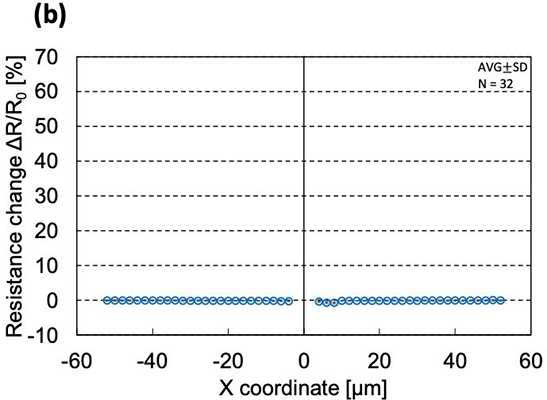

このTEGウエハを用いて、薄化ウエハ用のステルスダイシングプロセスの一種であるSDBG[用語6]プロセスを想定し、ウエハ厚50 µmとしたときのダメージ評価を実施した。Siに対する波長透過率の影響を評価するために2種類のレーザー(1,099 nm, 1,342 nm)を用いた。このダメージ評価の結果を図2に示す。波長1,342 nmでは、加工中心近傍の配線抵抗が大きく増加し、この部分でダメージが発生した(図2a)。一方1,099 nmでは、配線抵抗値が増加してないことから、ダメージが発生しないことを確認した(図2b)。この新たな評価手法により、波長1,099 nmのレーザーによって、ダメージレスのステルスダイシングが可能であることが明らかになった。

図2. ダイシング後の配線抵抗値:(a)波長1,342 nm、(b)波長1,099 nm

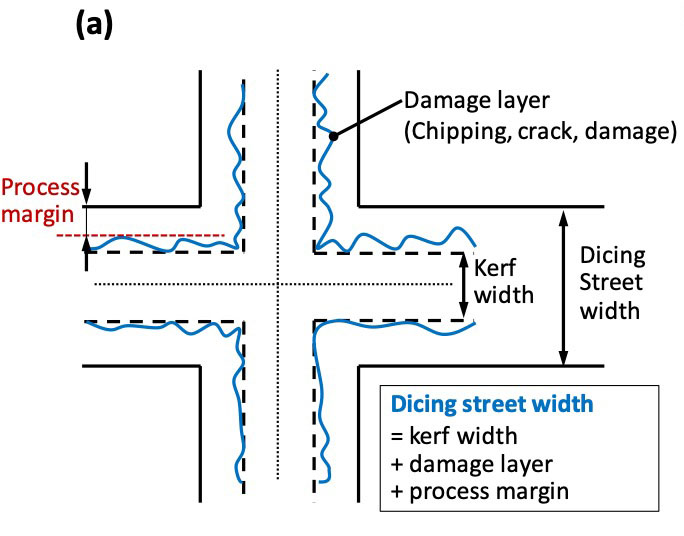

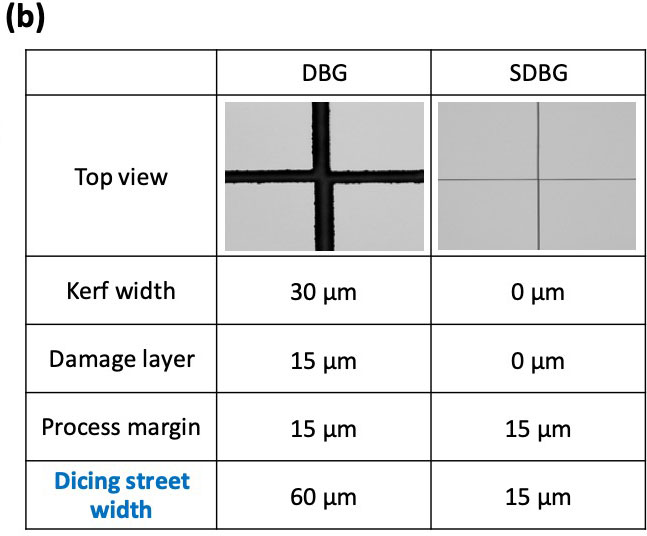

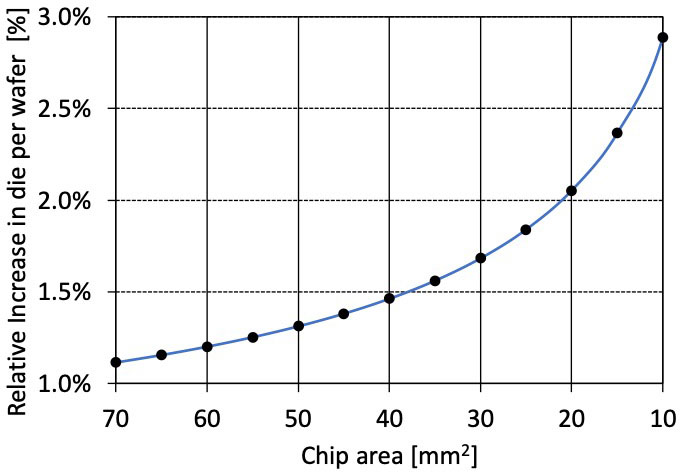

このダメージレスのステルスダイシング法で必要なダイシングストリート幅を、従来のダイシング法であるDBG[用語7]と比較した。その結果、DBGでは60 µmであったダイシングストリート幅が、SDBGでは15 µmとなり、1/4に削減できることが確かめられた(図3b)。さらに、チップ面積に対する、ダイシングストリート幅の削減によるチップ収率の増加率を計算したところ、チップ面積が小さくなるほどストリート幅の削減効果が大きいことが分かった(図4)。

図3. ダイシングストリート幅:(a)概略図 、(b)DBGとSDBGの比較

図4. ストリート幅を60 µmから15 µmに削減したときのチップ数の増加率

今回開発されたステルスダイシング技術は、ダイシングストリート幅が従来技術より縮小し、チップ収率を向上させることから、ウエハ製造プロセスの効率化に貢献することが期待される。今後は、このダメージレスダイシング技術の実用化に向けて、波長1,099 nmレーザー専用の光学エンジンの製品化を目指す。

用語説明

[用語1] WOWアライアンス : 東京工業大学を中心に設計・プロセス・装置・材料など、半導体関連の複数企業および研究機関からなる研究グループ。薄化したウエハを簡単に積層することができ、バンプレスTSV配線を用いた3次元化技術を世界で初めて開発に成功した。

[用語2] ステルスダイシング : パルスレーザーをウエハ内部に集光し、制御した亀裂を生成することによってウエハを分割する手法。非接触加工であるため、チッピングを抑制しながら、高速加工が可能。従来手法に比べて加工品質・精度が改善できるため、薄化ウエハのダイシングに適用されている。

[用語3] TEG : Test Element Groupの略であり、ICやLSIなどの設計・製造上の問題を見つけ出すための評価用チップ。

[用語4] ダイシングストリート幅 : ダイシングにより分割するためにチップ間に設けられた削りしろ。チッピングやカーフ幅、プロセスマージンに基づいて設計される。

[用語5] TSV : Through-Silicon-Viaの略であり、シリコンウエハを貫通させ、埋め込み配線で上下チップチップを接続させる接続孔。最近では、シリコン材料以外にも配線するため、前工程における垂直配線(vertical interconnects)とした方が分かりやすい。

[用語6] SDBG : Stealth Dicing Before Grindingの略であり、元厚のウエハの裏面からステルスダイシングを行い、その後ウエハを裏面研削して、チップ分割するプロセスのことである。薄化チップの狭ストリート化とチップ強度の向上を実現する。

[用語7] DBG : Dicing Before Grindingの略であり、先にウエハをハーフカットした後、裏面研削によりチップ分割する技術のことである。チップ分割時の裏面チッピングを抑制できる。

論文情報

|

学会名 :

|

IEEE 70th Electronic Components and Technology Conference (ECTC2020)

|

|

論文タイトル :

|

Damage-Less Singulation of Ultra-Thin Wafers using Stealth Dicing

|

|

発表者 :

|

Natsuki Suzuki, Tomoji Nakamura, Yuta Kondo, Shimpei Tominaga, Kazuhiro Atsumi, and Takayuki Ohba

|

お問い合わせ先

研究に関すること

東京工業大学 科学技術創成研究院 異種機能集積研究ユニット

秘書 沼澤文恵

E-mail : numazawa.f.aa@m.titech.ac.jp

Tel : 045-924-5866

取材申し込み先

東京工業大学 総務部 広報・社会連携課

E-mail : media@jim.titech.ac.jp

Tel : 03-5734-2975 / Fax : 03-5734-3661