東工大ニュース

東工大ニュース

公開日:2023.07.11

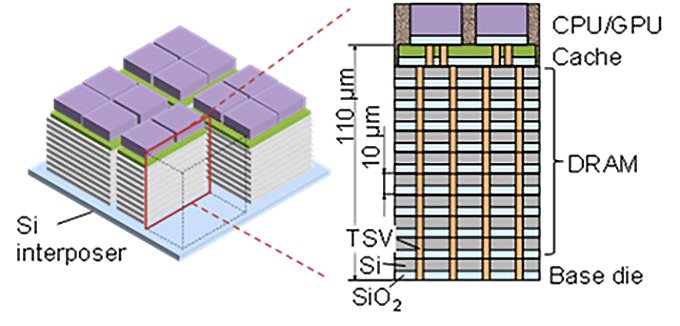

東京工業大学 科学技術創成研究院 異種機能集積研究ユニットの大場隆之特任教授は、WOWアライアンス[用語1]との共同研究により、バンプレスChip-on-Wafer(COW)[用語2]プロセスおよびWafer-on-Wafer(WOW)[用語3]プロセスによってCPU/GPUとメモリを3次元実装するハイブリッド3次元実装技術「BBCube 3D」を創出した。

現在、2次元的な配線でのデータ伝送能力の向上が、物理的、消費電力的に困難となる中、さらなる高帯域化を目指した3次元積層半導体の開発が進められている。しかし、従来の3次元積層技術はチップの垂直配線Through Si Via(TSV)[用語4]同士の接続にマイクロバンプ[用語5]を用いることから垂直配線の高密度化が難しく、また、データ伝送時の消費電力増大の一因となる寄生容量[用語6]の低減が困難という問題があった。

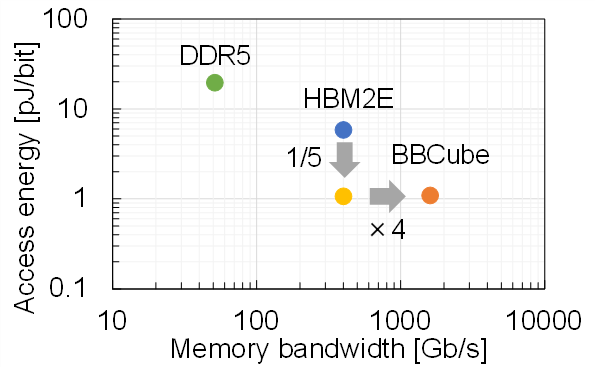

BBCube 3DのバンプレスCOW、WOWプロセスは、銅(Cu)を配線に用い、埋め込み・研磨によって垂直配線を行うCuダマシンTSV配線を用いることでバンプレス化し、垂直配線の16倍の高密度化、1/20の寄生容量低減を実現できる。さらにCPU/GPUとメモリを16,000本もの信号線で超並列に接続する。BBCube 3Dのデータ伝送はPCサーバ用メモリの13倍、AIなどに使われる高帯域メモリ(HBM2E)の4倍となる高帯域を実現しながら、電力はPCサーバ、高帯域メモリそれぞれに対し1/20、1/5に抑えることができることを世界で初めて明らかにした。

この成果は2023年6月11日~ 6月16日に開催の半導体回路・実装技術に関する国際会議「VLSI Symposium 2023」(主催:IEEE)で発表された。

AIやHPC(High Performance Computing)ではCPU/GPUとメモリとの間で大量のデータ伝送することが要求される。これに応えるためにデータ伝送のスピードを1秒間に100億ビットまで増加させ、Siインターポーザ[用語7]で多くのデータを送受する場合、4千~6千本までの配線を必要としていた。しかし、従来の2次元的な配置では配線数をこれ以上増やすことは物理的に難しい。また、伝送距離とデータ伝送速度に比例した消費電力の増大が課題となっている。

こうした2次元的な配置の限界を突破し、半導体デバイスのさらなる高性能化、低消費電力化を実現するために、CPU/GPUとメモリとを3次元積層するハイブリッド3次元実装技術の開発が急ピッチで進められている。

しかし従来の3次元積層による半導体パッケージでは、チップの垂直配線(TSV)同士の接続にマイクロバンプを用いており、垂直配線の高密度化やデータ伝送消費電力増大の一因となる寄生容量の低減が困難という問題があった。

本研究では、銅(Cu)を配線に用い、埋め込み・研磨によって垂直配線を行うバンプレスプロセスを用いてCPU/GPUとメモリとを3次元積層するBBCube 3Dを提案することで、AI HPC向け半導体のCPU/GPUとメモリ間データ伝送の高帯域と消費電力低減の両立を目指した。

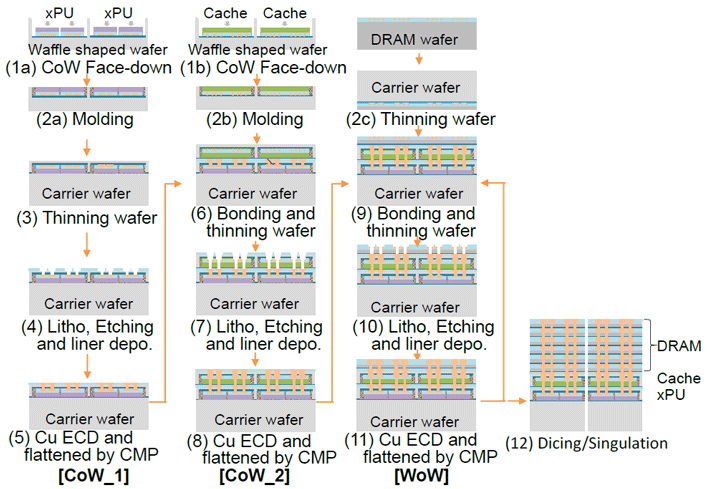

本研究におけるバンプレスWOW、COWプロセスの流れを説明する(図1)。チップとチップのTSV垂直配線はVia-Last法(Via-Last)[用語8]を用いている。

まず、ワッフル状にしたウエハであるワッフルウエハ[用語9]にCPUまたはGPUのチップを搭載し(図1-1a)、モールディングして(図1-2a)、ウエハを薄化(図1-3)、TSVを形成する(図1-4, 5)。同様にキャッシュチップをワッフルウエハに搭載し(図1-1b)、モールディングして(図1-2b)、CPU/GPUのウエハに積層し薄化する(図2-6)。その後TSVを形成してCPU/GPUとキャッシュとを接続する(図1-7, 8)。DRAMはDRAMウエハをキャリアウエハに貼付け、薄化する(図1-2c)。その後、CPU/GPU、キャッシュを搭載したウエハに積層し(図1-9)、TSVを形成して、キャッシュとDRAMを接続する(図1-10, 11)。図1-9から図1-11を繰り返してDRAMを必要層数積層した後、ダイシングして個別のチップに分ける。

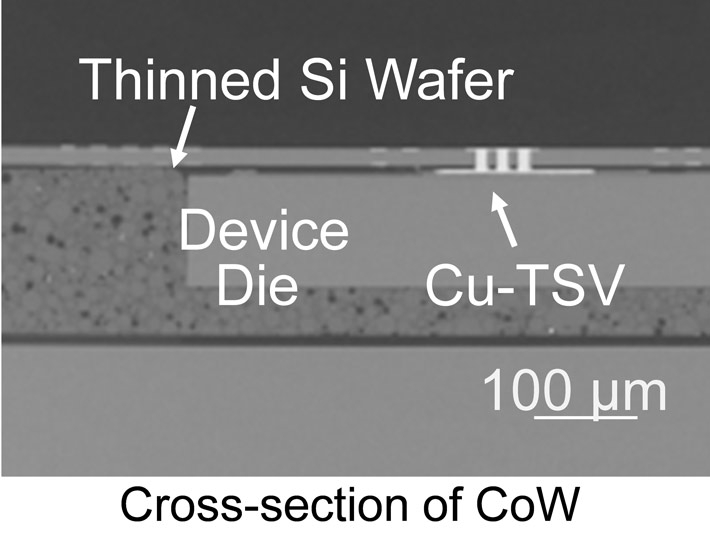

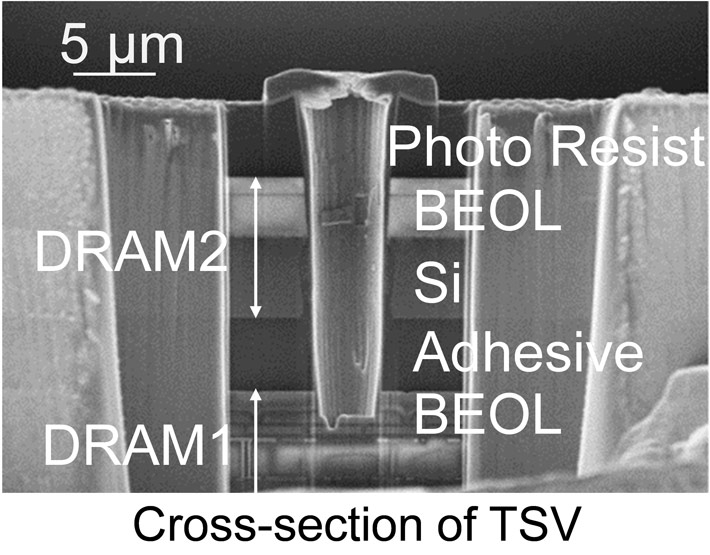

本研究で検証を進めているWOW、COWプロセスの断面写真を図2に示す。

図1. バンプレスWOW、COWプロセスフロー

図2. バンプレスWOW、COWの断面写真

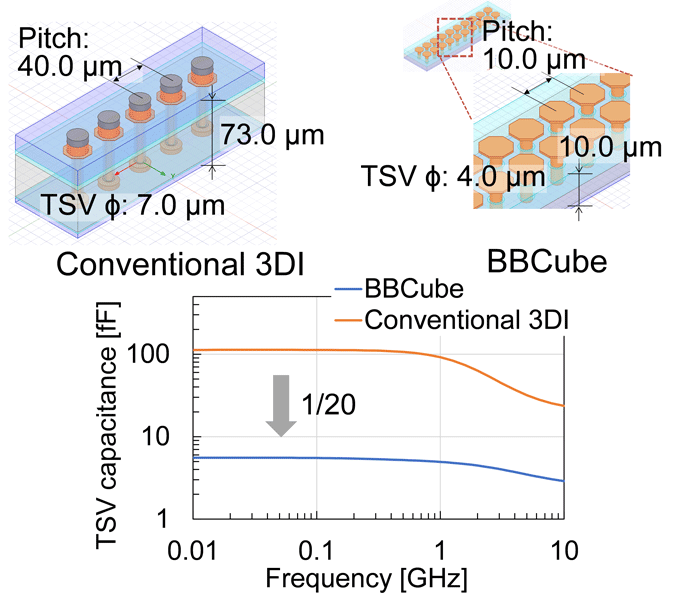

BBCubeの垂直配線(TSV)の寄生容量を3次元電磁界解析を用いて計算した。モデルと結果を図3に示す。BBCubeのTSVは従来の3次元実装のTSVに対し16倍の密度を実現しながら1/20の寄生容量となる。BBCubeのTSVの寄生容量はSi上に2次元的に配置した配線の長さに換算すると、わずか30 μm分の寄生容量に過ぎない。従来CPU/GPUとメモリの間は、配線長さを短くできるSiインターポーザを用いたものでも600 μmある。つまりCPU/GPUを垂直に配置してBBCube 3DのTSVを介して接続することで、配線の寄生容量を1/20に減らすことができ、データ伝承消費電力を低減することができる。さらにCPU/GPUを垂直に配置すると、CPU/GPU間を接続するTSVは面で配置することができる。チップサイズ(側壁の長さ)で制限されていた従来の実装に対し、BBCube 3Dは、CPU/GPUとメモリを16倍の16,000本もの信号線で超並列に接続することができる。BBCube 3Dの構成を図4に示す。

図3. 垂直配線(TSV)モデルと寄生容量計算結果

図4. BBCube 3Dの構成

CPU/GPUとメモリ間のデータ伝送にかかるエネルギーを解析し、PC/サーバ用メモリ(DDR5)、AIなどに使われる高帯域メモリ(HBM2E)との比較を行った。結果を図5に示す。BBCube3DはDDR5の13倍、HBM2Eの4倍の高帯域なデータ伝送を実現しながら、電力はそれぞれに対し1/20、1/5に抑えることが可能となる。

図5. データ伝送容量とデータ伝送にかかるエネルギー

微細化とともに300兆円まで巨大化した半導体産業は、各国の経済安全保障、社会インフラすべてわたって要になっている。微細化技術の発展は限界を迎えつつあり、DRAMやCPUデバイス単体の競争力は小さくなり、異なるデバイスをまとめたシステムの大量生産が次の競争力となっている。本技術は、半導体産業の悩みである微細化の終焉に応えるものであり、次世代半導体システムの道を示すものである。特に性能と生産性の両輪が求められる半導体産業において、300 mmウエハプロセスを軸に開発された三次元集積技術は、社会実装に直結し、高い競争力を得ることができる。

同技術は本学拠点の産学アライアンスで開発されたものであり、技術と組織、それぞれのシームレス化、柔軟な開発計画に基づく。半導体において国プロによらない産学協調開発は初めての試みである。

今回開発したBBCube 3Dにより、AI、HPC用半導体の電力を大幅に低減することが可能となる。今後は、CPU/GPUとメモリをバンプレスWOW、COWで積層したBBCube 3Dを試作し、大容量データ伝送と低消費電力の両立の実証を目指す。

用語説明

[用語1] WOWアライアンス : 東京工業大学を中心とした産学研究プラットフォーム。半導体関連の設計・プロセス・装置・材料などを手がける企業、および研究機関によって構成される。高度かつ簡便なウエハの薄化技術・積層技術を持ち、バンプレスTSV配線を用いた3次元化技術を世界で初めて開発に成功した。

[用語2] Chip-on-Wafer(COW) : チップをウエハ上に接合する技術。一般的にチップの接合は、樹脂材料でできた配線基板に対して行われており、それと区別するために「ウエハ上に(Chip-on-Wafer)」という表現が用いられている。チップをウエハ上に接合することにより、以降の半導体製造工程において、各種装置を用いた高精度な加工が行えるようになる。

[用語3] Wafer-on-Wafer(WOW) : ウエハ上にウエハを接合する技術。COWと同様の技術であるが、多くのチップが形成されたウエハ同士を接合することにより、同時に多数のチップの積層ができ、COWよりも効率よい。ただしチップのサイズは同一である必要があるため、メモリ等同一チップを積層する場合に向く。

[用語4] Through-Silicon-Via(TSV) : シリコン(Silicon)ウエハを貫通(Through)させて開けた接続孔(Via:ビア)。上下に積層したチップを、埋め込み配線によって接続させる。最近では、シリコン材料以外にも配線するため、前工程における垂直配線(vertical interconnects)とした方が分かりやすい。

[用語5] マイクロバンプ : 電極部に半田で形成した配線接続のための突起。半田を溶かして圧力をかけて接合させるため、隣のバンプと短絡しないよう間隔が必要。

[用語6] 寄生容量 : 電圧のかかった導体の間に、設計の意図から外れて発生する電気的な負荷。

[用語7] Siインターポーザ : 半導体のパッケージにおいて、端子ピッチが異なる半導体とパッケージ基板の間を中継するSi製の電源基板。主に、ハイエンド向け半導体のパッケージにおいて用いられる。

[用語8] Via-Last法 : チップ間の電気配線接続方法の1つ。チップやウエハを積層した後にエッチング加工で接続孔を形成し、Cuなどの金属をスパッタとメッキで充填して配線として利用する。従来はVia-Firstとよばれ、チップに予めCu金属を埋設しておき、チップやウエハ同士を積層する際に、同時に金属と金属を機械的に接触させ、熱処理や圧縮応力を利用して導通界面を形成する。Via-Lastは前工程、Via-Firstは実装由来の方式であり、微細化と高信頼性配線にはVia-Lastが用いられる。

[用語9] ワッフルウエハ : その名の通り菓子の「Waffle」を由来としたウエハ表面の加工形状で、ウエハ表面に四角い溝を規則的にエッチング加工したものである。ドライエッチングの最適化で幾何学的な段差と平坦な底部を形成し、接着層を塗布後、底部にチップをFace-down でボンディングする。ボンディングが完了したらモールディングし、モールド材料とチップ裏面のシリコンを同時に研削、そして平坦化する。チップで専有された四角い溝の残りがモールド体積となる。

論文情報

学会名 : |

IEEE 2023 Symposium on VLSI Technology and Circuits (2023 VLSI Symposium) |

論文タイトル : |

Bumpless Build Cube (BBCube) 3D: Heterogeneous 3D Integration Using WoW and CoW which Enables TB/s Bandwidth with Low Bit Access Energy |

発表者 : |

Norio Chujo, Koji Sakui, Shinji Sugatani, Hiroyuki Ryoson, Tomoji Nakamura and Takayuki Ohba |

お問い合わせ先

東京工業大学 科学技術創成研究院 異種機能集積研究ユニット

秘書 川島

Email kawashima.t.ae@m.titech.ac.jp

Tel 045-924-5866

取材申し込み先

東京工業大学 総務部 広報課

Email media@jim.titech.ac.jp

Tel 03-5734-2975 / Fax 03-5734-3661