東工大ニュース

東工大ニュース

公開日:2022.01.31

東京工業大学 元素戦略研究センターの金正煥(Junghwan Kim、キム・ジョンファン)助教、細野秀雄栄誉教授らは、溶液の塗布法を用いた高性能pチャンネル薄膜トランジスタ(TFT)の開発に成功した。

ディスプレイなどに用いられるTFTにおいて近年もっとも注目されているのが、n型半導体として機能するアモルファス酸化物半導体InGaZnO(IGZO)であり、既に高精細液晶ディスプレイや有機ELテレビなどで広く実用化されている。さらに、昨今では論理回路などに必要となるCMOS[用語1]の応用にも期待がかかるが、そのためにはn型半導体と対をなすp型半導体の機能向上が必要不可欠である。

今回の研究では、ペロブスカイト型ハロゲン化物の優れた輸送特性に着目し、2次元ペロブスカイトのPEA2SnI4と、3次元ペロブスカイトのFASnI3という2つの物質の両方の長所を発現させる微細構造をデザインした。両者は「移動度とキャリア制御性[用語2]」において相反する特性を示し、小さい電界移動度もしくはスイッチオフが出来ないといった問題点を抱えているが、今回開発した方法では両者の利点を生かし、欠点を補い合うことに成功した。結果的に、従来の酸化物TFTに匹敵する移動度25 cm2/VsのpチャンネルTFTを実現させた。さらに、IGZO TFTと組み合わせることで非常に優れたCMOSとして機能することが確認できた。また、今回開発したp型半導体材料は鉛などの有害物質を含まないため、環境負荷や人体への健康影響が小さいことも特徴である。

本研究成果はドイツ科学誌「Advanced Science」に2021年12月22日付で公開された。

電気自動車・ウェアラブルデバイス・プリンタブルデバイスなどの開発や普及が進み、あらゆるものがコンピュータを内蔵し、インターネットにつながる時代を迎えようとしている。その中で欠かすことができないのが、コンピュータの駆動や計算を担う集積回路の高性能化である。集積回路の機能を担うCMOSと呼ばれる半導体素子は、nチャンネルおよびpチャンネルトランジスタを組み合わせることでつくられる。これらnおよびpチャンネルトランジスタはn型およびp型半導体材料などで構成され、各半導体物質の機能性や製造・加工コスト、安全性や安定性が、CMOSをはじめとする半導体素子の機能や価格を大きく左右する。

n型半導体においては、2004年のアモルファス酸化物InGaZnO(IGZO)を用いた薄膜トランジスタ(TFT)の開発が、技術発展の重要な転換点となった。IGZO-TFTは従来のシリコン系TFTに比べて、コンピュータの処理速度等に関わるキャリア移動度が10倍以上高く(10~15 cm2/Vs)、しかも均質で大面積な薄膜を低温で容易に作製できるという優位性を持つため[参考文献1]、現在は有機ELディスプレイや高精細ディスプレイなどに実用化されている。

一方で、p型半導体に関しても新規材料の模索が進められてきたが、未だ画期的な進展には至っていない状況にある。そこで本研究では視点を変えて、まったく新しい物質を見出すのではなく、既存の物質同士をうまく組み合わせることで優れた半導体特性を実現することを試みた。

半導体として求められる特性にはいくつかあるが、基本的かつ重要なものとして「キャリア制御性(現実的な閾値電圧[用語3]で電流がオン/オフできること)」と「キャリア移動度(オンにした際の電流の流れやすさ)」が挙げられる。この2つにおいて高い性能を併せ持つp型半導体物質の探索は難航していた。

本研究で着目したのは金属ハロゲン化物(ヨウ化物)半導体であり、非常に大きいイオン半径をもつヨウ素の存在が優れたp型半導体特性をもたらすことが過去の研究で示されている[参考文献2]。さらにこれらの半導体の溶液を塗布するだけで薄膜作製が可能であることから、低温かつ安価なプロセスでのTFT作製への応用が期待できる物質である。中でも今回採用したのは、PEA2SnI4(フェニチルアンモニウムイオン・スズ・ヨウ素からなる2次元構造化合物)およびFASnI3(ホルムアミジウムイオン・スズ・ヨウ素からなる3次元構造化合物)の2つであり、いずれもペロブスカイト型の結晶構造を持つ。

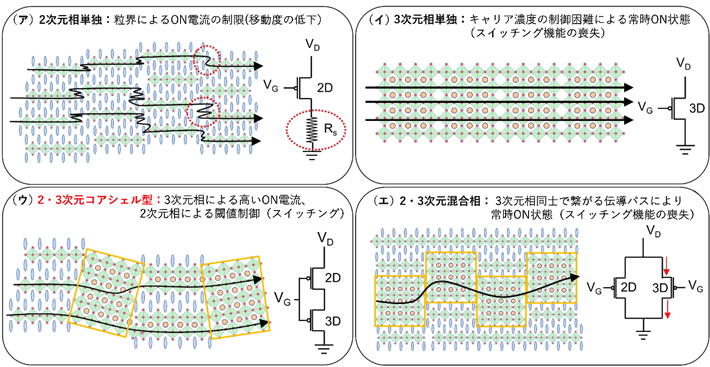

それぞれの物質の特性としては、PEA2SnI4は良好なキャリア制御性を有するが、電気抵抗が高くキャリア移動度が低いことが難点となっている(図1ア)。一方でFASnI3は高いキャリア移動度を持つが、キャリア濃度の制御が難しく、常に電流オンの状態になってしまうことが半導体材料としての活用を妨げている(図1イ)。本研究では、この2つの物質を混在することで微細構造を制御することで、それぞれの利点は生かしつつ、欠点を補い合うことができるのではないかと考えた。

材料設計のコンセプトとして、図1ウに示すような、キャリアが3次元相と2次元相の両方を通過して電流が流れる構造(コア-シェル構造)をつくることが必要であると仮説立てた。もしキャリア移動度が高い3次元相同士が隣接してしまうと(図1エ)、図1イと同様に常時電流オン状態になってしまうため、3次元相が2次元相によって完全に隔離されているような図1ウの構造になるよう、実際に薄膜作製の条件検討を行なった。

PEA2SnI4およびFASnI3を含む溶液を塗布したのちに、加熱・真空処理を行うことで薄膜を作製した。この時、PEA2SnI4とFASnI3の比率や、添加物の有無や量が、生成する薄膜にどのように影響するか検討した。

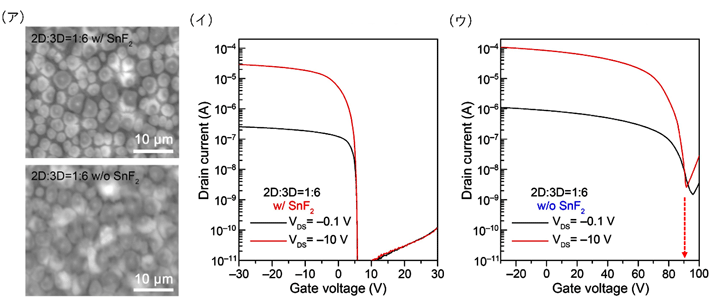

結果的に、2次元相(PEA2SnI4)と3次元相(FASnI3)を1:6の比で混ぜた溶液に微量(2 mol%)のフッ化スズ(SnF2)を添加することでコア-シェル構造が得られることが明らかとなった(図2ア)。得られたTFT特性からはコア-シェル構造の優位性が明確であり、図2イに示したように約5 V付近の閾値電圧でスイッチングしていることがわかる。一方、SnF2添加剤を用いずに作製されたTFTは約90 Vの非常に高い閾値電圧を示し、これは非現実的な値である(図2ウ)。これは図1エに示したように、3次元相(FASnI3)のみで繋がったパスによって得られた結果だと考えられる。

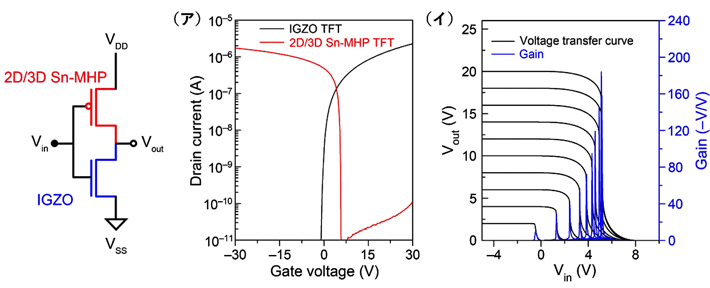

図3は従来のnチャンネルIGZO-TFTと新たに開発されたpチャンネル2・3次元ペロブスカイトTFTを組み合わせたCMOSインバータの特性を示している。最終的に2次元相(PEA2SnI4)と3次元相(FASnI3)の比を1:9にすることで25 cm2/Vsと非常の高い電界効果移動度が得られた。これは従来のIGZO TFTと同等な値であることがわかる(図3ア)。作製されたCMOSインバータからは約180 V/V(VDD=20 V)の非常に高いゲインが得られた(図3イ)。これはこれまでに報告されたIGZO TFTを用いたCMOSの中では非常に高い値である。

図3. (ア)IGZO TFTと2・3次元ペロブスカイトTFTの伝達特性(イ)CMOSインバータの電圧伝達特性

本研究では、溶液を使って低温で作製可能な高性能pチャンネルTFTを実現する新たな手法を提唱した。今回の成果は、次世代エレクトロニクスに向けて溶液法を用いることの優位性と今後の方向性が明確にされたと考えられる。これまで、溶液法から作製された薄膜および電子デバイスは真空プロセスより性能がかなり劣るという点がよく指摘されてきた。しかし、今回の研究で実証された複合相およびコア-シェル型構造薄膜を、従来の真空プロセスを用いて作製することは非常に難しい。溶液法ならではの新たな方向性が見出されたといえる。さらに、従来のnチャンネル酸化物TFTと組み合わせた高性能CMOSの実証はウェアラブルやフレキシブルエレクトロニクスの社会実装に繋がるものと期待される。

一方、実用に向けて、ペロブスカイト型ハロゲン化物特有の大気中でも安定性の問題がまだ残っており、迅速な産学連携が必要だと考えられる。

付記

本成果は、以下の事業・研究課題によって得られた。

文部科学省 元素戦略プロジェクト<拠点形成型>

研究課題名:「東工大元素戦略拠点」

代表研究者:東京工業大学 元素戦略研究センター センター長 細野秀雄

PM:元素戦略研究センター 雲見日出也 特任教授

研究実施場所:東京工業大学

研究開発期間:平成25年7月~令和4年3月

科学技術振興機構(JST)戦略的創造研究推進事業 さきがけ

研究領域:「物質探索空間の拡大による未来材料の創製」

(研究総括:陰山洋 京都大学 教授)

研究課題名:ヨウ素アニオンの性質を生かした新機能の開拓

代表研究者:Kim Junghwan

研究実施場所:東京工業大学

研究開発期間:令和3年10月~令和7年3月

用語説明

[用語1] CMOS(Complementary Metal Oxide Semiconductor) : 論理回路を構成するために必要な素子。PチャンネルトランジスタとNチャンネルトランジスタを組み合わせたもの。

[用語2] キャリア制御性 : 半導体にはキャリアの極性によってp型もしくはn型半導体に分類される。さらに半導体は用途に応じてキャリア濃度を調整する必要性がある。例えば薄膜トランジスタ(TFT)では1015-1016 cm-3程度のキャリア濃度が適切。本研究でのキャリア制御性はキャリアの極性ではなく、後者のキャリア濃度のことを意味する。

[用語3] 閾値電圧 : TFTがオン/オフするスイッチング時の電圧を意味する。使用用途に応じた特定の電圧範囲の中でオン出来ない場合、常時オフ状態という。同様にオン出来ない場合、常時オフ状態という。

論文情報

掲載誌 : |

Advanced Sciecne |

論文タイトル : |

High-Performance P-Channel Tin Halide Perovskite Thin Film Transistor Utilizing a 2D–3D Core–Shell Structure |

著者 : |

J. Kim*, Y. Shiah, K. Sim, S. Iimura, K. Abe, M. Tsuji, M. Sasase, H. Hosono*(安部氏の所属はSilvaco Japan) |

DOI : |

お問い合わせ先

東京工業大学 元素戦略研究センター

助教 金正煥(Junghwan Kim、キム・ジョンファン)

E-mail : JH.KIM@mces.titech.ac.jp

Tel : 045-924-5197

東京工業大学 元素戦略研究センター

栄誉教授 細野秀雄

E-mail : hosono@mces.titech.ac.jp

Tel : 045-924-5009

取材申し込み先

東京工業大学 総務部 広報課

E-mail : media@jim.titech.ac.jp

Tel : 03-5734-2975 / Fax : 03-5734-3661